Справочные материалы

1. Цифровые микросхемы

Краткое содержание.

Предисловие

Широкое внедрение цифровой техники в радиолюбительское творчество связано с появлением интегральных микросхем. Цифровые устройства, собранные на дискретных транзисторах и диодах, имели значительные габариты и массу, ненадежно работали из-за большого количества элементов и особенно паяных соединений. Интегральные микросхемы, содержащие в своем составе десятки, сотни, тысячи, а в последнее время многие десятки и сотни тысяч и даже миллионы компонентов, позволили по-новому подойти к проектированию и изготовлению цифровых устройств. Надежность отдельной микросхемы мало зависит от количества элементов и близка к надежности одиночного транзистора, а потребляемая мощность в пересчете на отдельный компонент резко уменьшается по мере повышения степени интеграции.

В результате на интегральных микросхемах стало возможным собирать сложнейшие устройства, изготовить которые в радиолюбительских условиях без применения микросхем было бы совершенно невозможно.

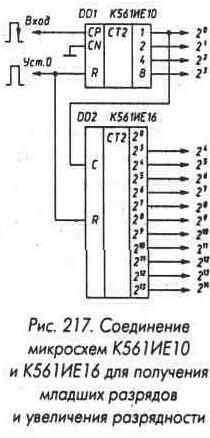

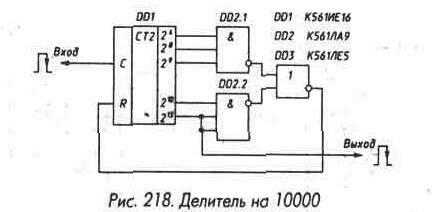

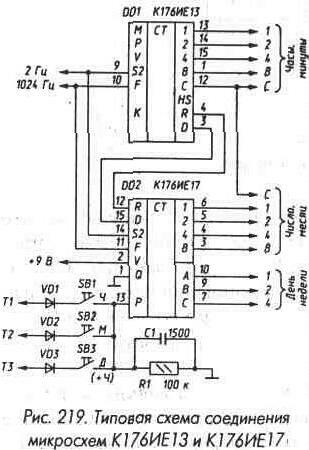

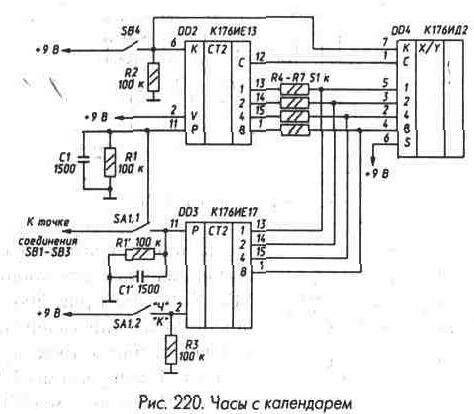

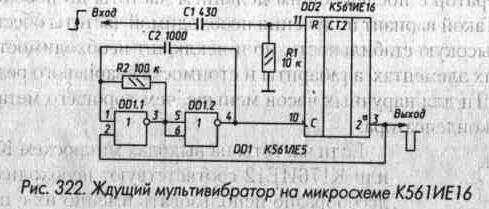

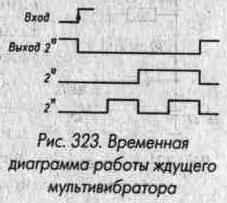

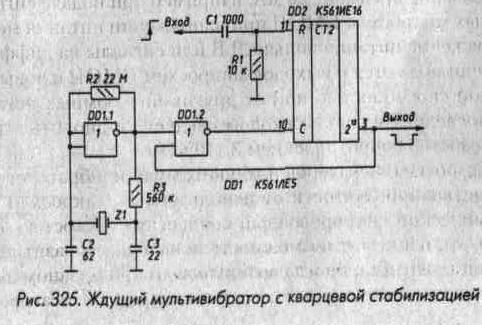

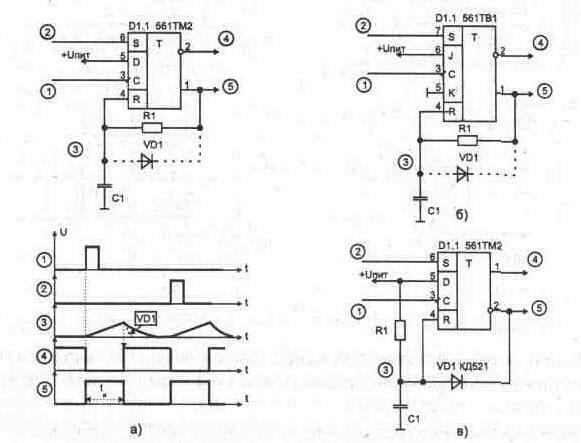

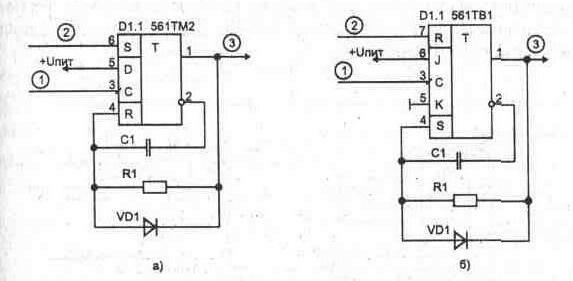

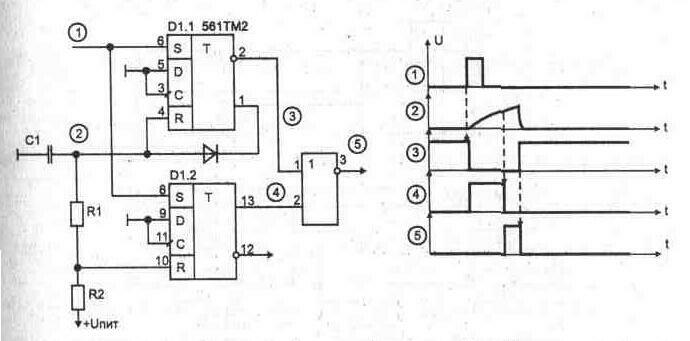

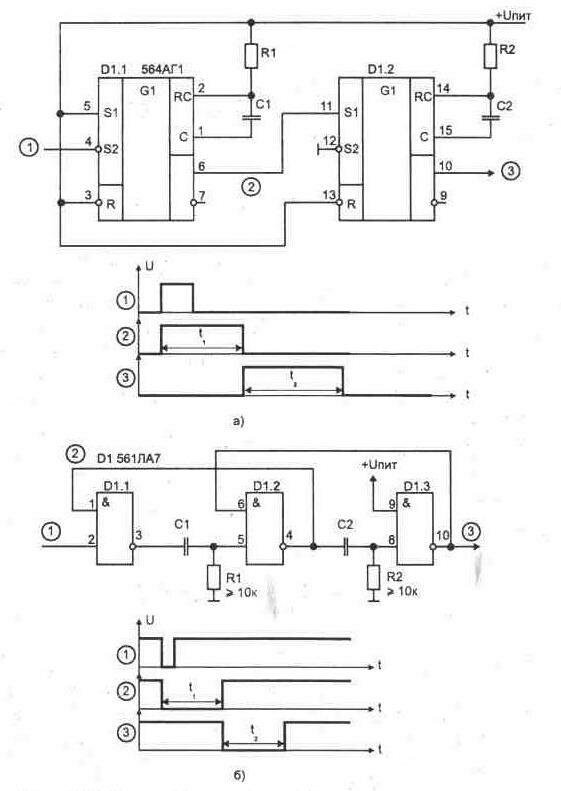

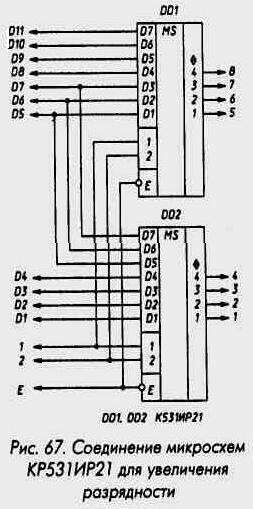

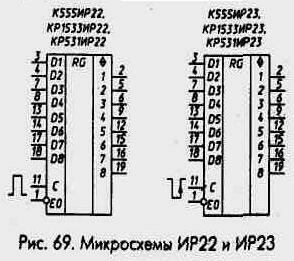

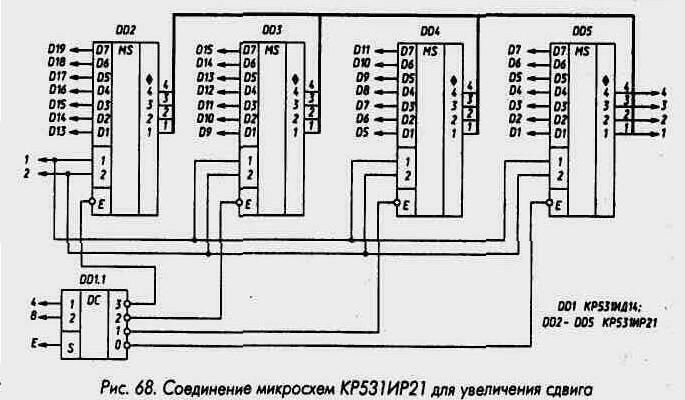

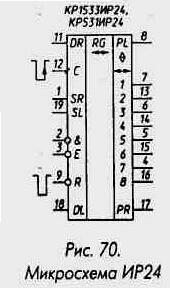

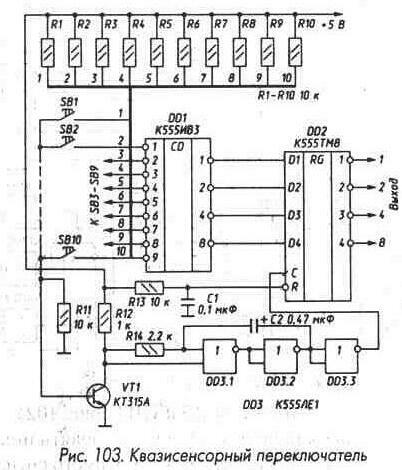

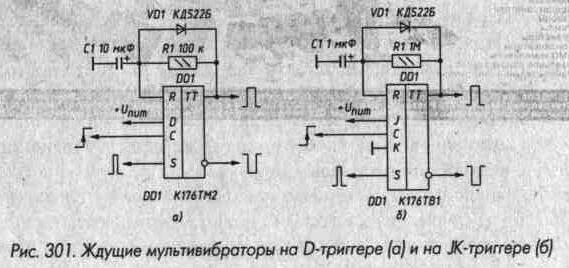

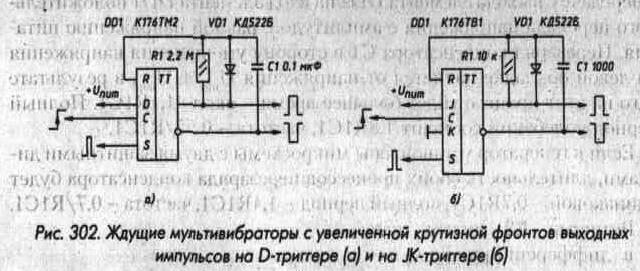

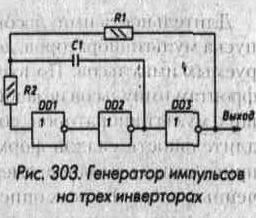

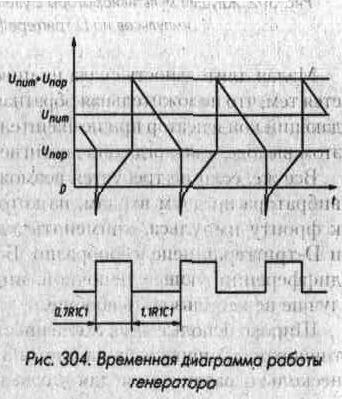

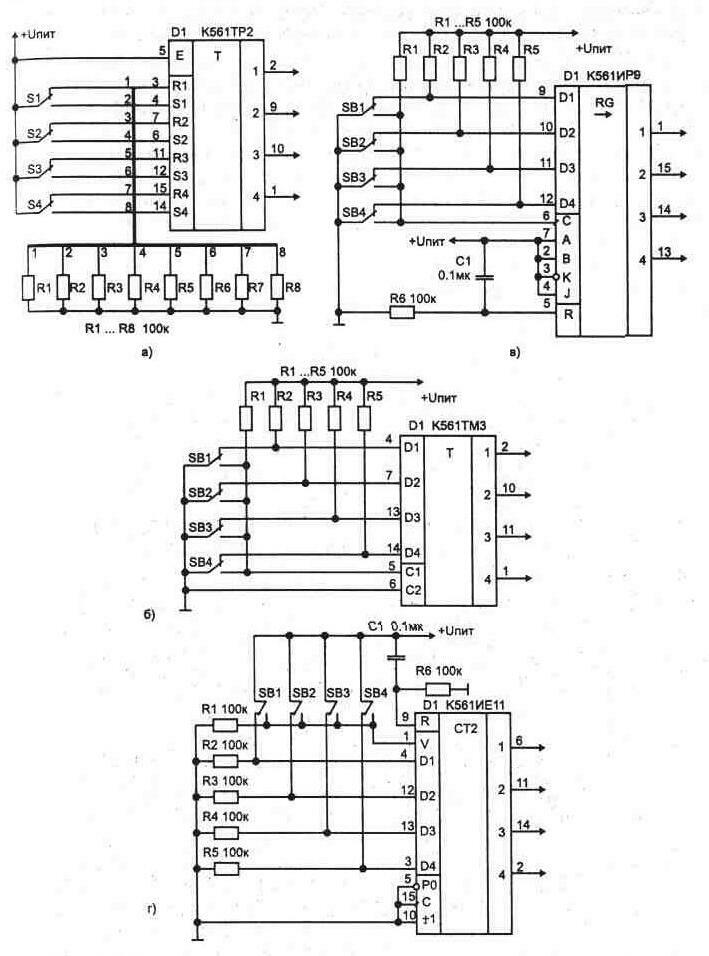

Книга написана на основании большого опыта автора по изучению и применению микросхем серий ТТЛ К155, К555, КР531, КР1533, серий КМОП К176, К561, КР1554, КР1561,564 и содержит материал, частично нашедший отражение в его статьях, опубликованных в журнале «Радио» в 1982-1998 гг., и книгах автора. В настоящем издании описаны общие принципы функционирования комбинационных, последовательностных микросхем, ждущих мультивибраторов и генераторов, приведены схемы соединения микросхем для увеличения разрядности, фрагменты принципиальных схем цифровых устройств с применением различных описываемых микросхем, приведены описания формирователей и генераторов импульсов, квазисенсорных переключателей.

Автор надеется, что данная книга поможет многим радиолюбителям и радиоспециалистам творчески подойти к самостоятельной разработке и изготовлению многих полезных цифровых устройств.

* Под псевдонимом С. Алексеев.

1. Микросхемы серии ТТЛ.

Глава 1.Микросхемы серии ТТЛ.

1.1 Общие сведения.

1.1. Общие сведения

У нас в стране обширна номенклатура выпускаемых интегральных микросхем. Для построения устройств автоматики и вычислительной техники широкое применение находят цифровые микросхемы серии К 155, которые изготавливают по стандартной технологии биполярных микросхем транзисторно-транзисторной логики (ТТЛ). Имеется свыше 100 наименований микросхем серии К 155. При всех своих преимуществах - высоком быстродействии, обширной номенклатуре, хорошей помехоустойчивости - эти микросхемы обладают большой потребляемой мощностью. Поэтому им на смену выпускают микросхемы серии К555, принципиальное отличие которых - использование транзисторов с коллекторными переходами, зашунтированными диодами Шоттки. В результате транзисторы микросхем серии К555 не входят в насыщение, что существенно уменьшает задержку выключения транзисторов. К тому же они значительно меньших размеров, что уменьшает емкости их р-n-переходов. В результате при сохранении быстродействия микросхем серии К555 на уровне серии К155 удалось уменьшить ее потребляемую мощность примерно в 4...5 раз.

Дальнейшее развитие микросхем серий ТТЛ - разработка микросхем серии КР1533. Основное эксплуатационное отличие их от схем серии К555 - в 1.5...2 раза меньше потребляемая мощность при сохранении и повышении быстродействия.

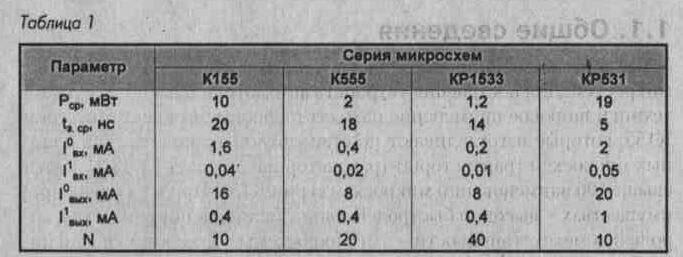

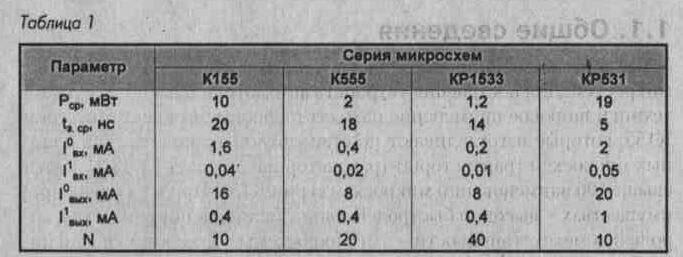

Средняя задержка распространения элементов микросхем серии К155, К555, КР1533 примерно 15...20 нс. В случаях, когда требуется более высокое быстродействие, используют микросхемы серии КР531. Для сравнения основных параметров в табл. 1 приведены значения средней потребляемой мощности Рср и средней задержки tз.ср распространения микросхем ТТЛ указанных серий, а также стандартные значения входных Iвх и выходных Iвых токов и нагрузочной способности N указанных серий микросхем. Некоторые микросхемы допускают большие выходные токи и имеют большую нагрузочную способность, чем указано в табл. 1. Часть микросхем (особенно серии КР531) также имеют отличные от стандартных входные токи. Эти отличия специально указаны далее.

Стандартные выходные уровни лог. 1 составляют 2,4...2,7 В, лог. 0 -0,36...0,5 В.

Напряжение питания микросхем серий ТТЛ 5 В +-5%, для серии КР1533 допуск на напряжение питания +-;10%.

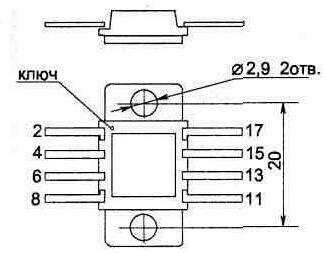

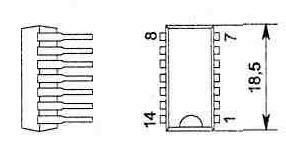

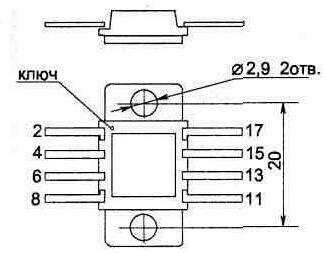

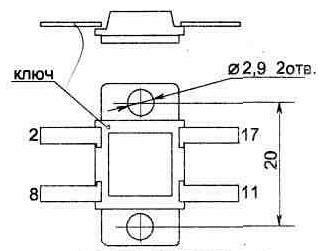

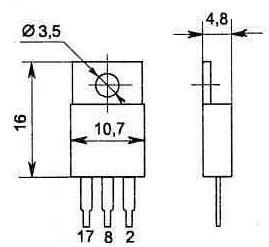

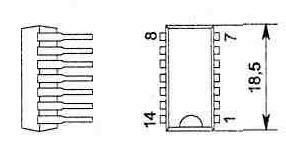

Микросхемы выпускают в пластмассовых корпусах с 8, 14, 16, 20, 24, 28 выводами, температурный диапазон их работоспособности:

-10...+70 °С. Часть микросхем серий К155 и К555 выпускают в керамических корпусах (их обозначение КМ155 и КМ555), температурный диапазон работоспособности таких микросхем -45...+85 °С.

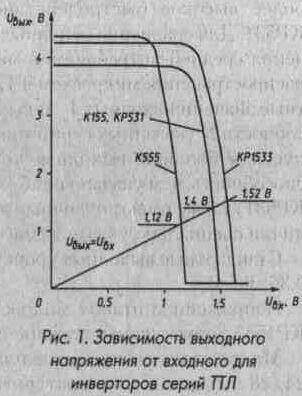

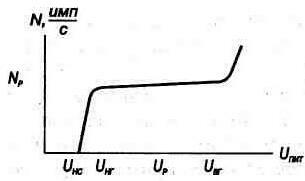

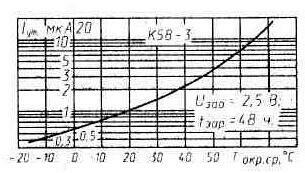

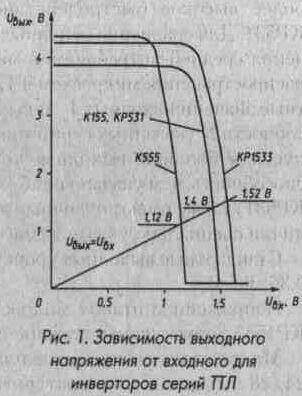

На рис. 1 приведены зависимости выходного напряжения от входного для инвертирующих логических элементов упомянутых серий микросхем при температуре +20 С. Поскольку за порог переключения принимается входное напряжение, при котором выходное равно ему, его нетрудно найти по приведенным зависимостям как точку пересечения с прямой Uвых = Uвх. Из рисунка видно, что микросхемы серии КР1533 имеют наибольший порог переключения - 1,52 В и, как следствие, наибольшую помехоустойчивость.

Рассматриваемые серии имеют в своем составе однотипные микросхемы с совпадающими после номера серии цифробуквенными обозначениями. Логика работы однотипных микросхем, за редким ис-

ключением, отмеченным далее, совпадает. Микросхемы серии КР531 ранее не имели в обозначении буквы «Р», а имели в конце обозначения букву <<П>>, например К531ЛАЗП.

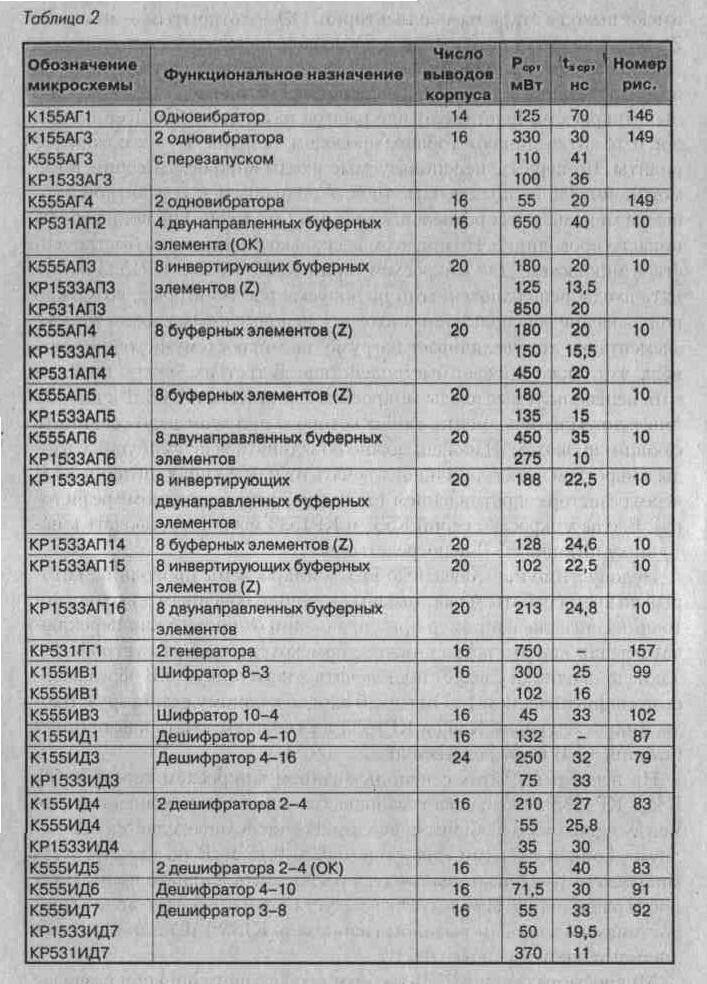

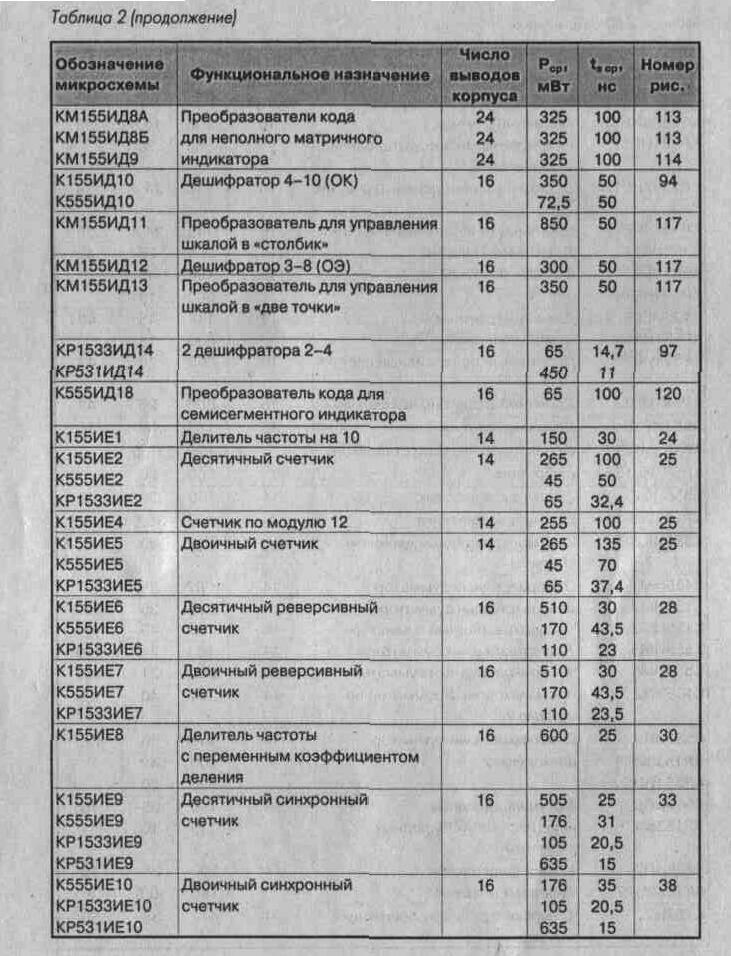

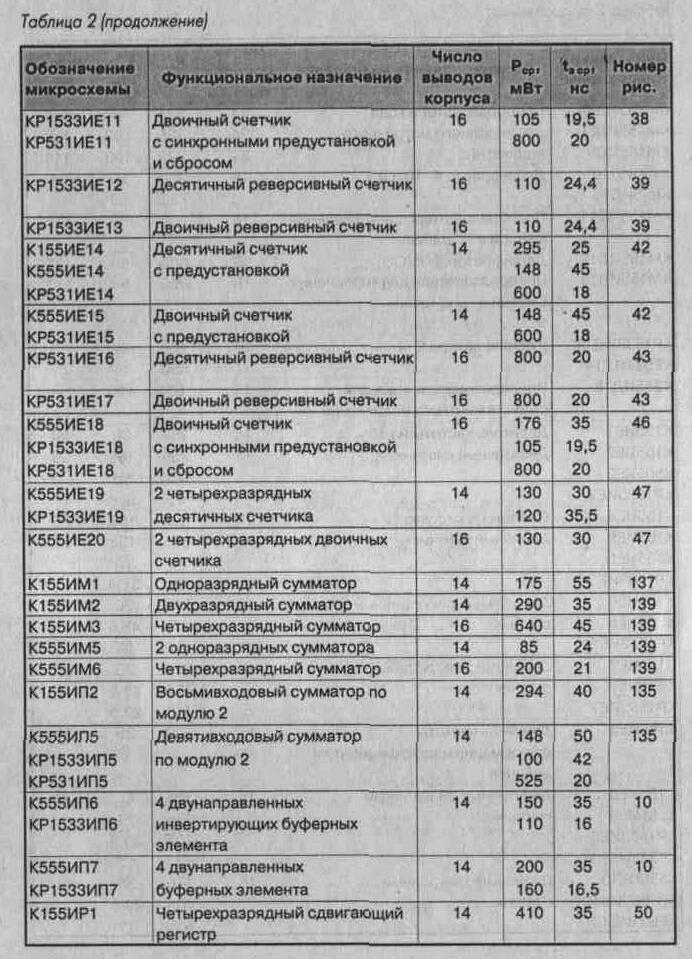

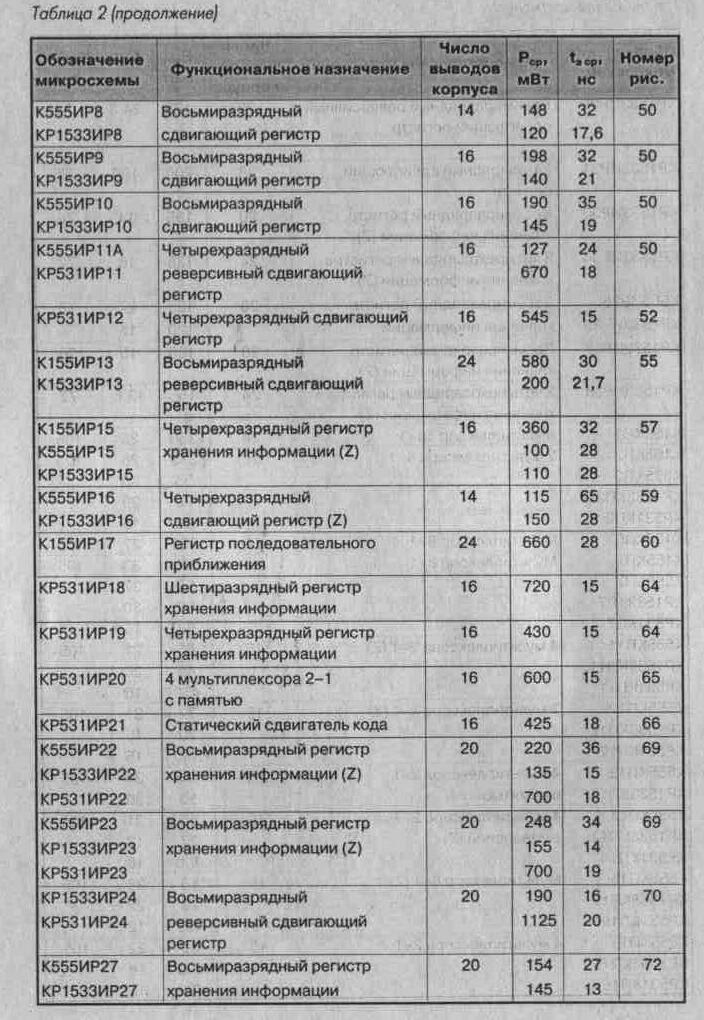

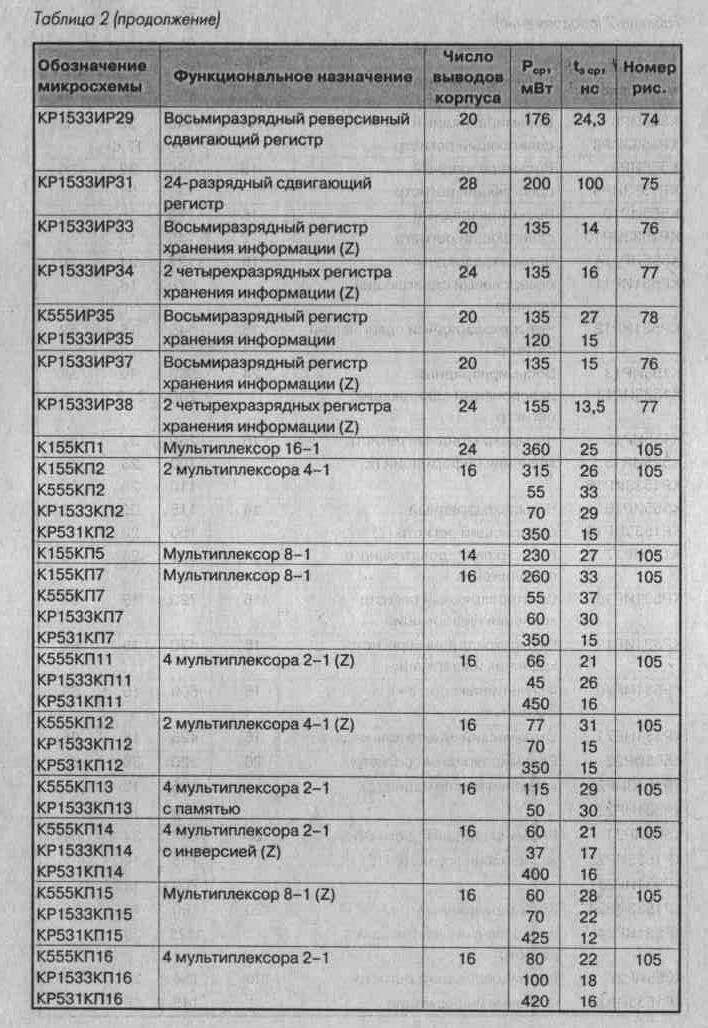

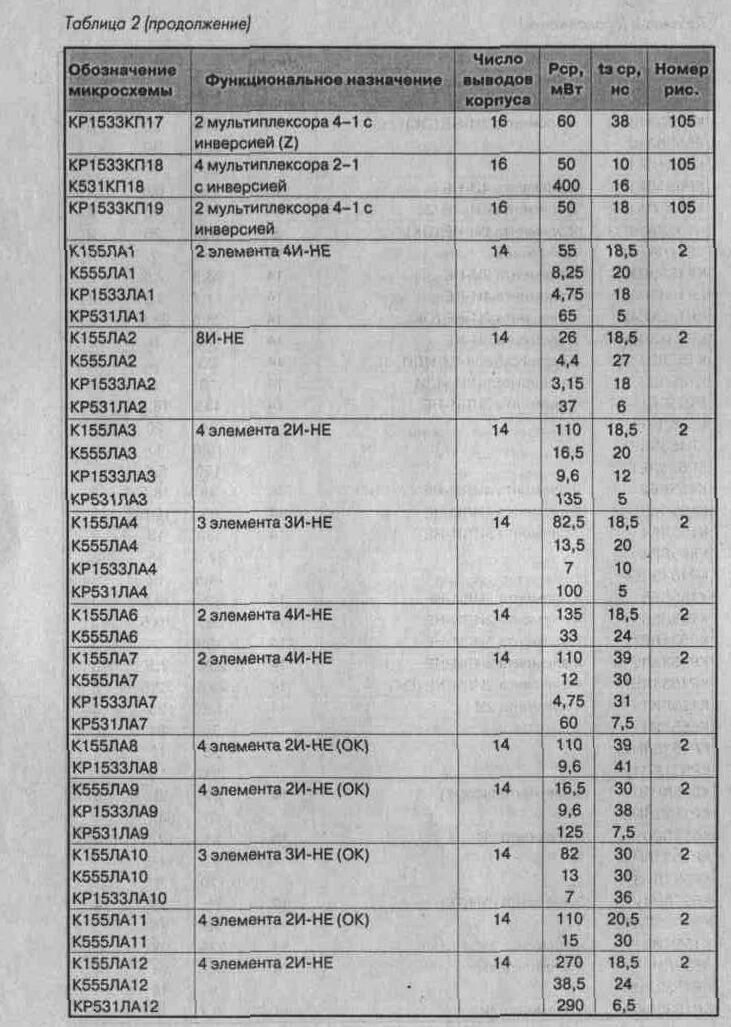

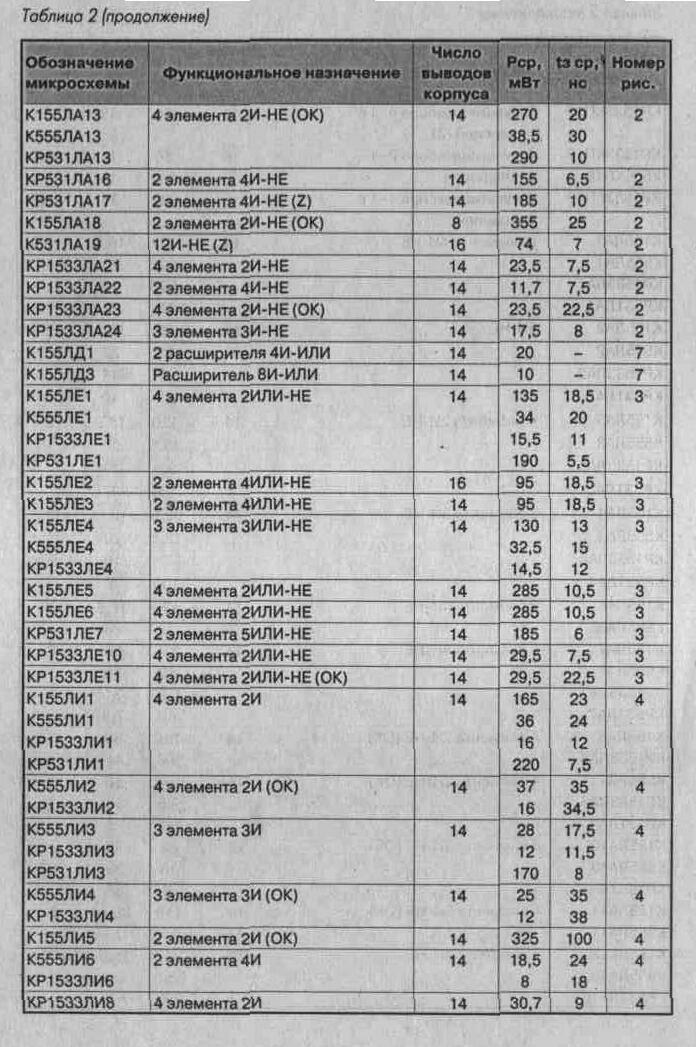

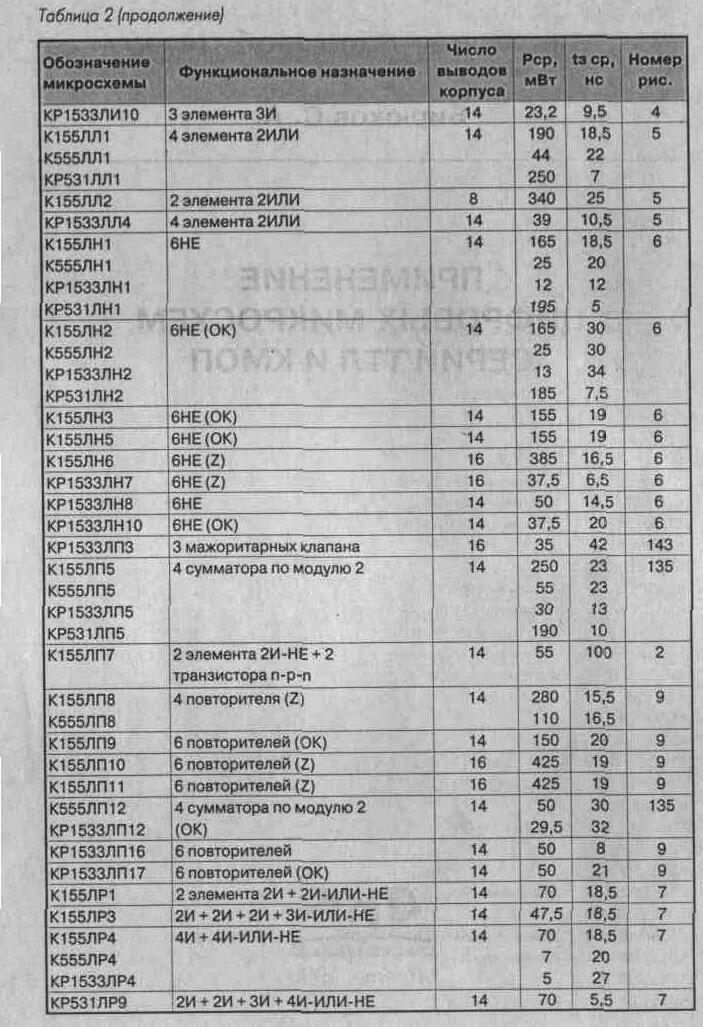

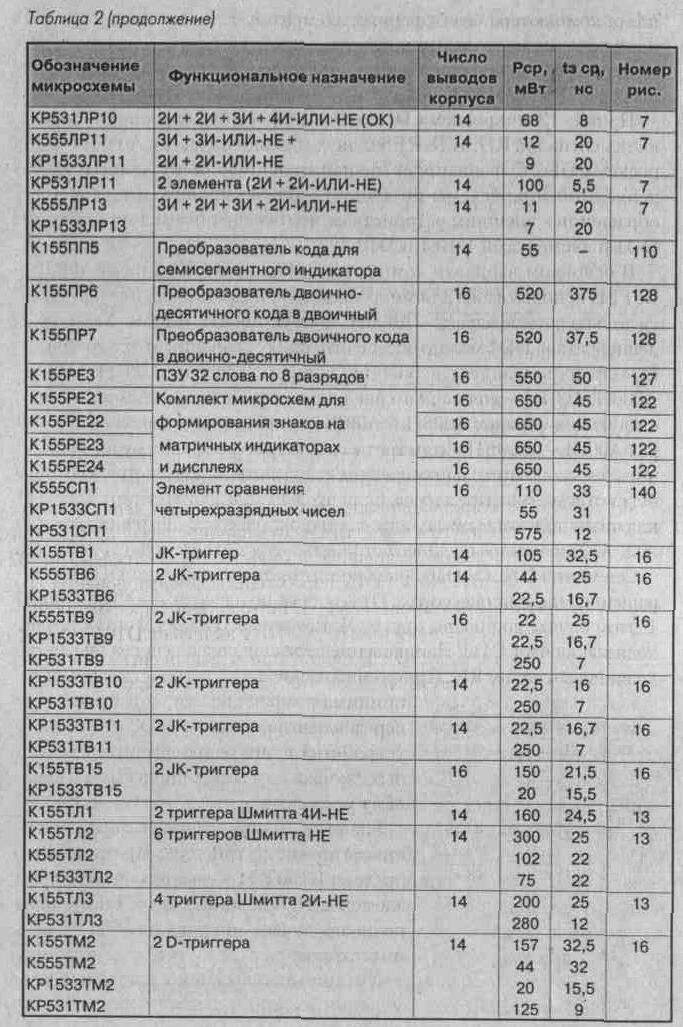

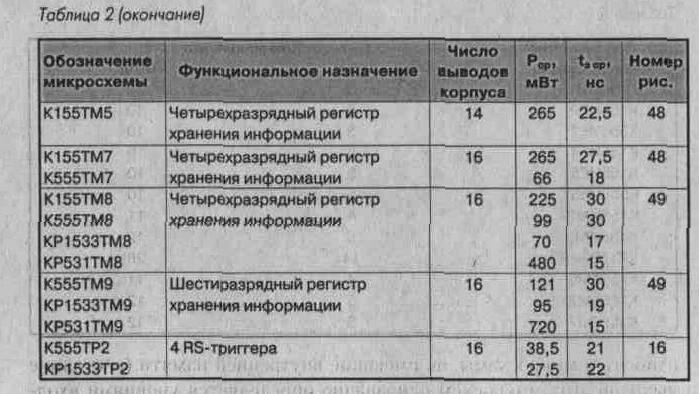

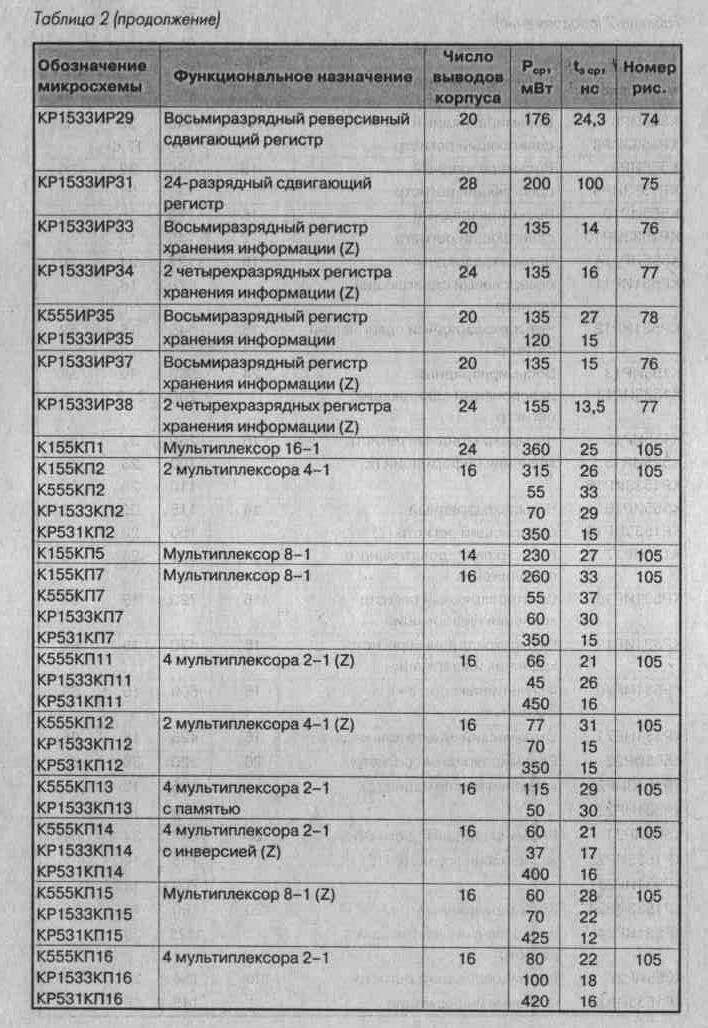

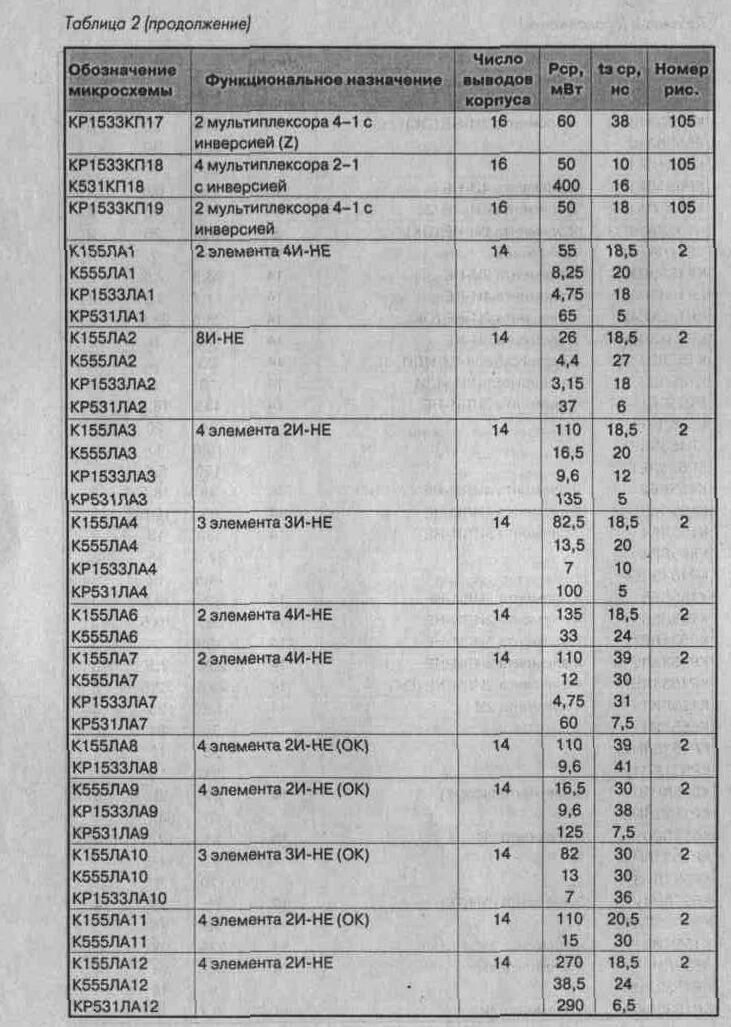

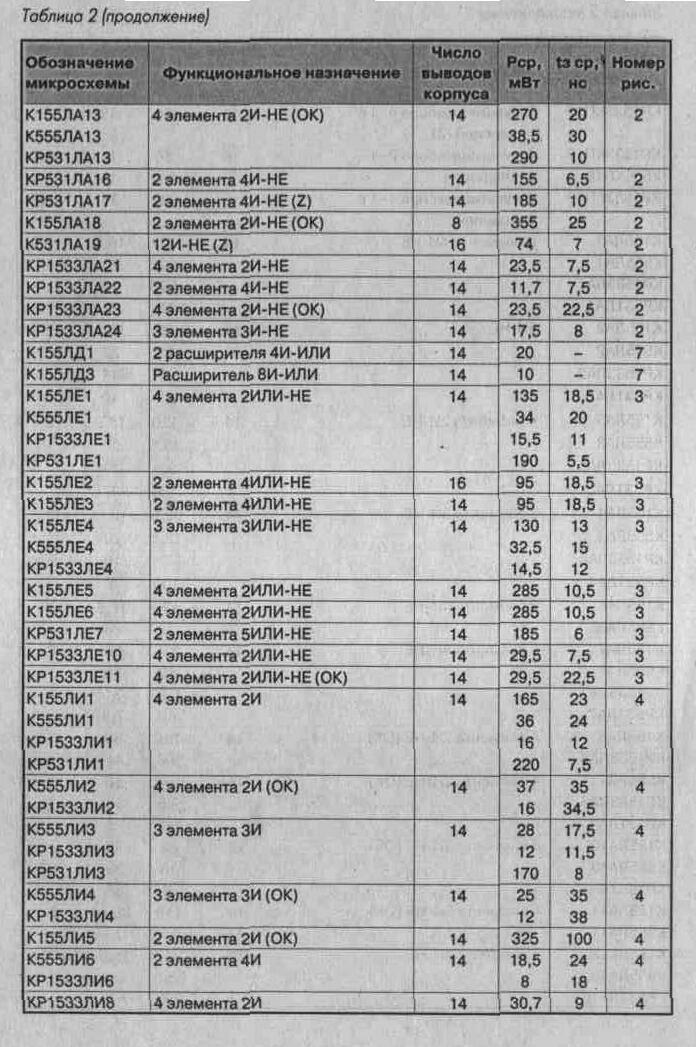

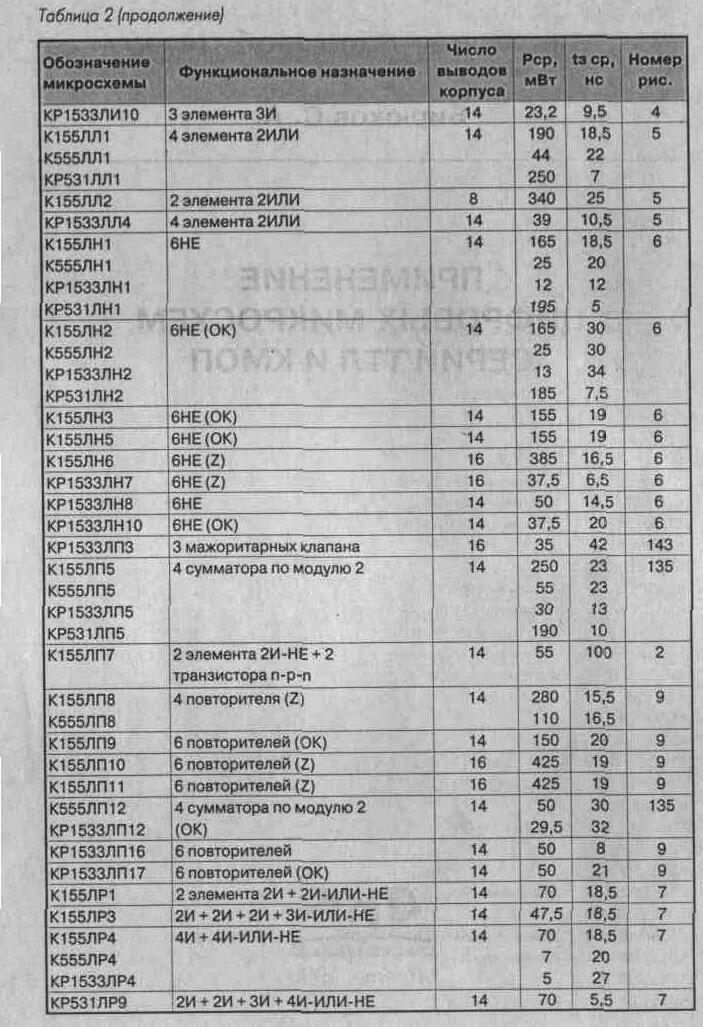

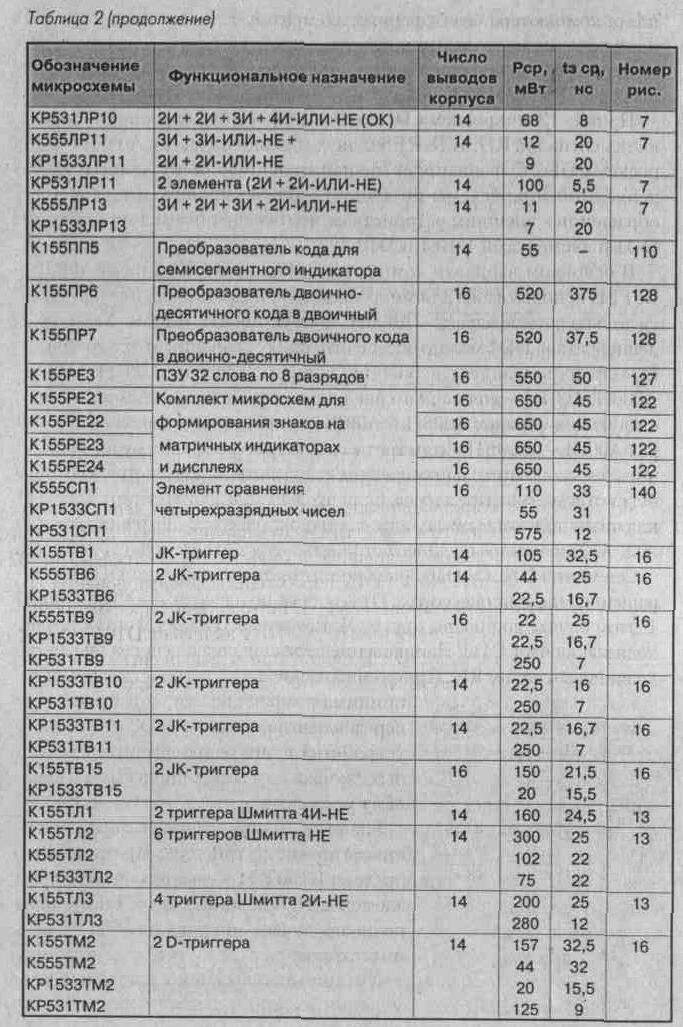

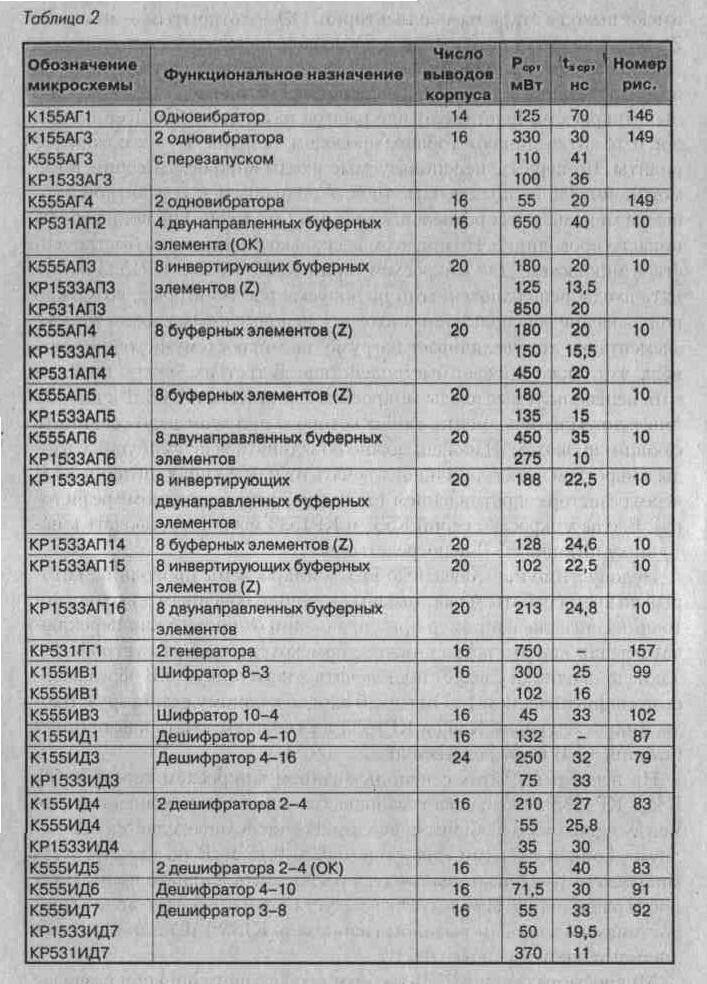

В табл. 2 приведены обозначение большинства рассматриваемых микросхем, функциональное назначение, число выводов корпуса, средняя потребляемая мощность, средняя задержка распространения сигнала и номер рисунка, на котором приведено графическое обозначение микросхемы.

В функциональном назначении буквы означают: OK - микросхемы

имеют выход с открытым коллектором, ОЭ - с открытым эмиттером, Z - выходы могут переводиться в высокоимпедансное состояние.

При разработке принципиальных схем различных устройств всегда возникает вопрос: что делать с- неиспользуемыми входами интегральных микросхем. Если по логике работы на вход необходимо подать лог. 0, то его соединяют с общим проводом, если лог. 1 - возможны варианты. Во-первых, неиспользуемые входы микросхем серии К155 можно никуда не подключать, то есть подпаивать к контактной площадке минимальных размеров, к которой (это важно) не подключены никакие проводники. Но при этом несколько уменьшается быстродействие микросхем. Для микросхем серий К555, КР531, КР1533 оставлять входы неподключенными не допускается. Во-вторых, возможно подключение неиспользуемых входов к используемым входам того же элемента, но это увеличивает нагрузку на микросхему-источник сигнала, что также снижает быстродействие. В-третьих, можно подключать неиспользуемые входы микросхем серий К155 и КР531 к выходу инвертирующего элемента, входы которого при этом надо соединить с общим проводом. Наконец, можно объединять неиспользуемые входы микросхем этих серий и подключать их к источнику питания +5 В через резистор сопротивлением 1 кОм (до 20 входов к одному резистору). Входы микросхем серий К555 и КР1533 можно подключать к источнику питания +5 В непосредственно.

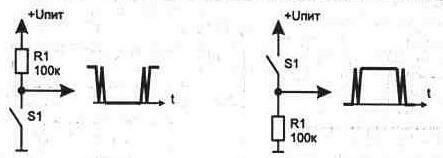

Недопустимо подключать ко входу микросхемы проводник, который во время работы может оказаться неподключенным к выходу источника сигнала, например при управлении от кнопки или переключателя, так как это резко снижает помехоустойчивость устройства. Такие проводники следует подключать к источнику +5 В через резистор сопротивлением 1 кОм (до 20 входов к одному резистору). Входы микросхем серий К555 и КР1533 можно подключать к источнику питания +5 В непосредственно.

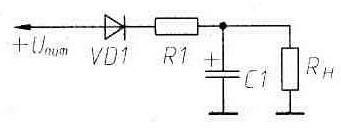

На печатных платах с использованием микросхем серий К155, К555, КР1533 необходима установка блокировочных конденсаторов между цепью +5 В и общим проводом. Их число определяется одним-двумя конденсаторами емкостью 0,033...0,15 мкВ на каждые пять микросхем. Конденсаторы следует располагать на плате по возможности равномерно. Их следует также установить рядом со всеми микросхемами с мощным выходом (например, К155ЛА6) или с потребляемой мощностью более 0,5 Вт.

Микросхемы серий КР531 требуют особого внимания при разводке цепей питания и общего провода. При изготовлении промышленных

устройств на микросхемах этой серии используют многослойные печатные платы, один из слоев используют в качестве общего провода, другой - в качестве шины питания. Если используют двухслойные платы, шины питания и общего провода выполняют навесными в виде латунных полос шириной около 5 мм, керамические блокировочные конденсаторы емкостью 0,047...0,15 мкФ подпаивают непосредственно к этим шинам (один конденсатор на одну-две микросхемы). В радиолюбительских условиях можно одну сторону печатной платы использовать под общий провод, другую - под сигнальные цепи и под провод питания, конечно, при этом придется устанавливать много перемычек и к каждой микросхеме блокировочный конденсатор.

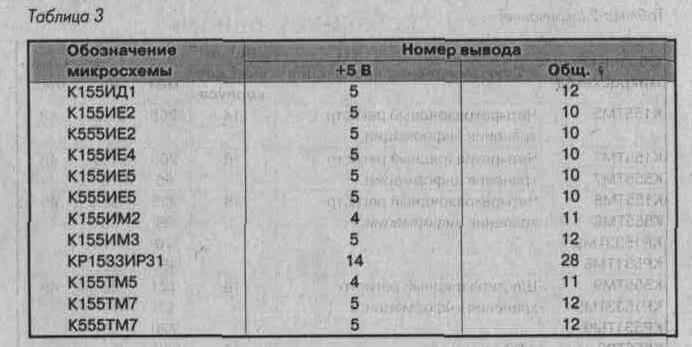

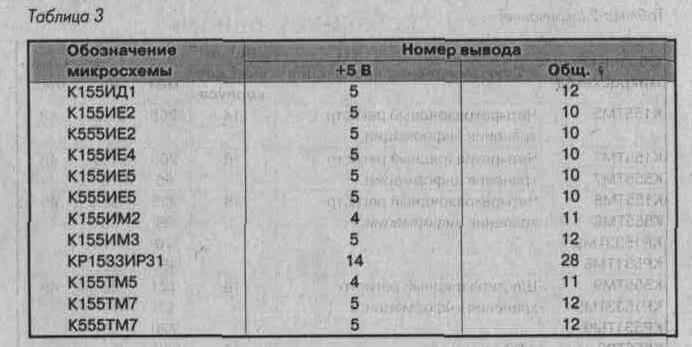

Как правило, напряжение питания микросхем подводят к выводу с максимальным номером, общий провод - к выводу, номер которого вдвое меньше. Случаи исключения из этого правила приведены в табл. 3.

Микросхемы серий К555 и КР1533 можно применять вместо однотипных микросхем серии К 155 и совместно с ними, при этом следует иметь в виду, что их нагрузочная способность на микросхемы серии К155 составляет 5. Микросхемы серии КР531 следует применять только в случае необходимости высокого быстродействия, так как они создают большой уровень помех, к которым особенно чувствительны микросхемы серии К555, и потребляют большую мощность.

Цифровые микросхемы по своим функциям делятся на два больших класса - комбинационные и последовательностные. К первому

относятся микросхемы, не имеющие внутренней памяти (состояние выходов этих микросхем однозначно определяется уровнями входных сигналов в данный момент времени). Ко второму - микросхемы, состояние выходов которых определяется не только уровнями входных сигналов в данный момент времени, но и последовательностью состояний в предыдущие моменты времени из-за наличия внутренней памяти.

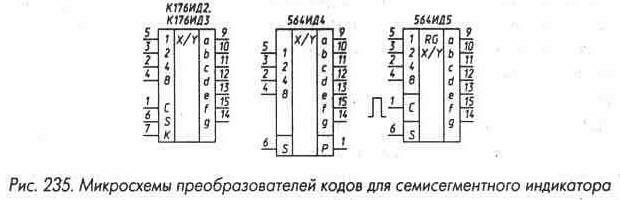

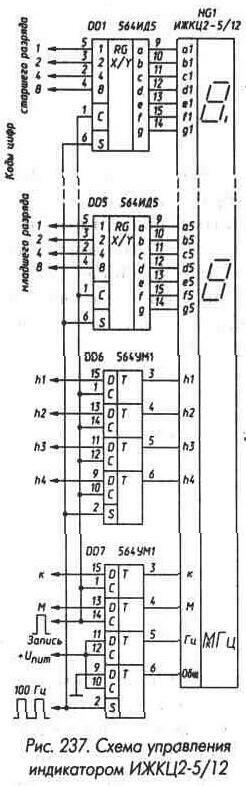

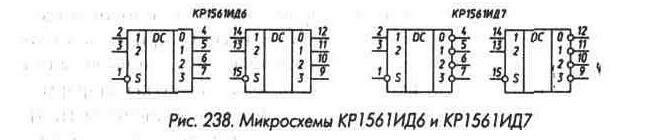

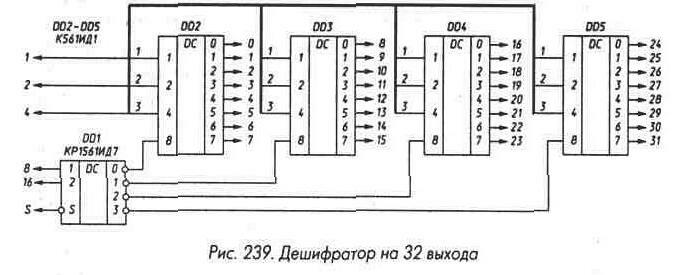

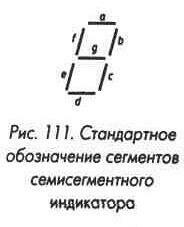

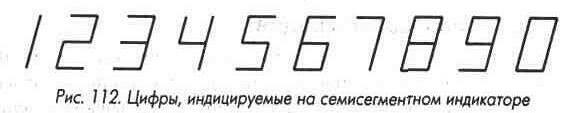

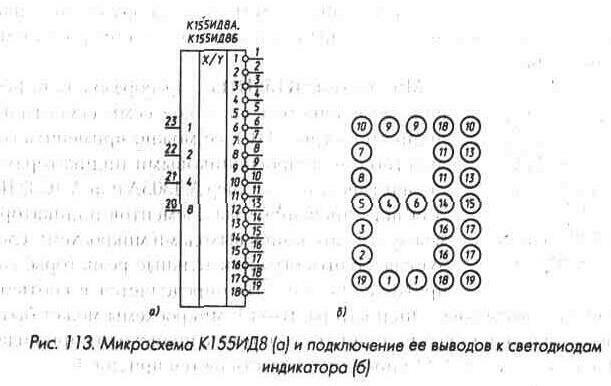

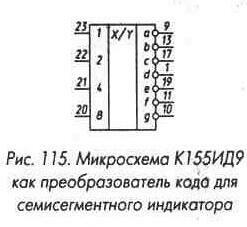

К комбинационным относятся простые логические микросхемы И-НЕ, И-ИЛИ-НЕ, НЕ, ИЛИ-НЕ, И, ИЛИ, более сложные элементы - дешифраторы, мультиплексоры, сумматоры по модулю 2, полные сумматоры, преобразователи кодов для семисегментных и матричных индикаторов, шифраторы, программируемые постоянные запоминающие устройства, преобразователи двоично-десятичного кода в двоичный и обратно, однонаправленные и двунаправленные буферные элементы, мажоритарные клапаны, триггеры Шмитта, которые, однако, имеют внутреннюю память и могут быть отнесены и к последовательностным микросхемам, а также некоторые другие.

К последовательностным микросхемам относятся триггеры, счетчики, сдвигающие регистры, оперативные запоминающие устройства и некоторые другие микросхемы.

Ждущие мультивибраторы нельзя отнести однозначно ни к одному из упомянутых классов, так как внутренняя память этих микросхем помнит изменение входных сигналов ограниченное время, после чего состояние выходов микросхемы ни от чего не зависит. То же самое относится и к генераторным микросхемам.

Рис. 1. Зависимость выходного напряжения от входного для инвертеров серий ТТЛ

Таблица 1. Температурный диапазон работоспособности микросхем

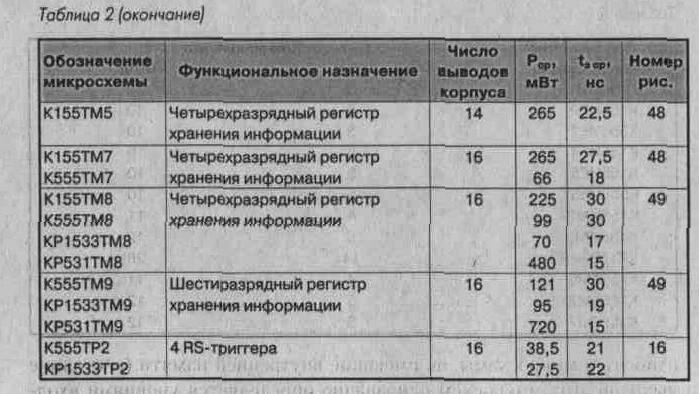

Таблица 2. Обозначение и технические характеристики микросхем ТТЛ (окончание)

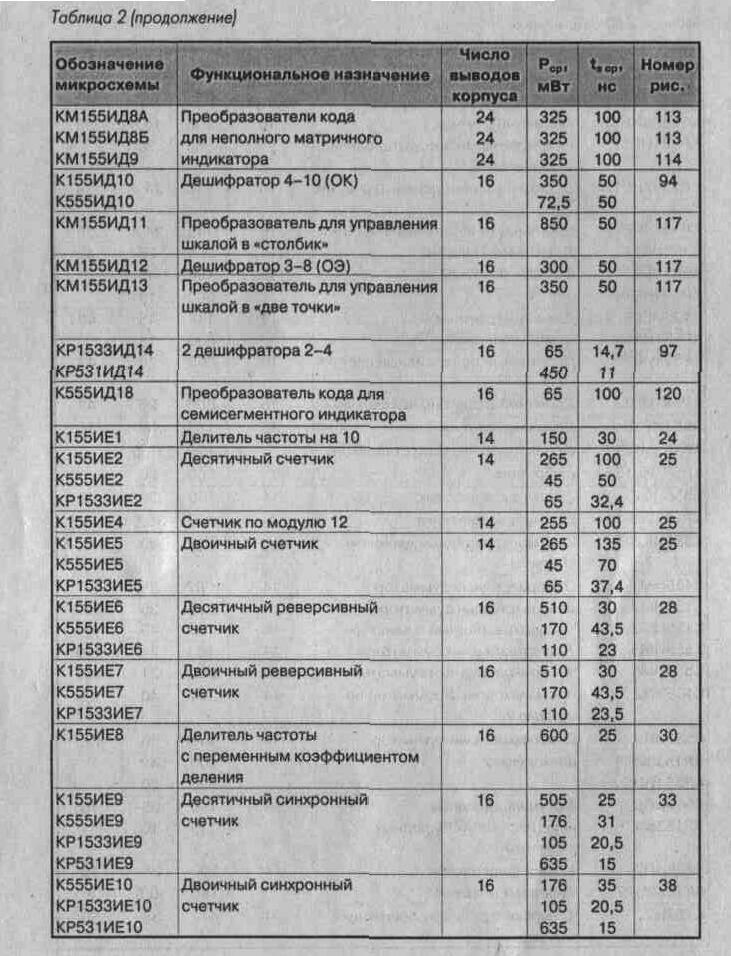

Таблица 2. Обозначение и технические характеристики микросхем ТТЛ (продолжение 1)

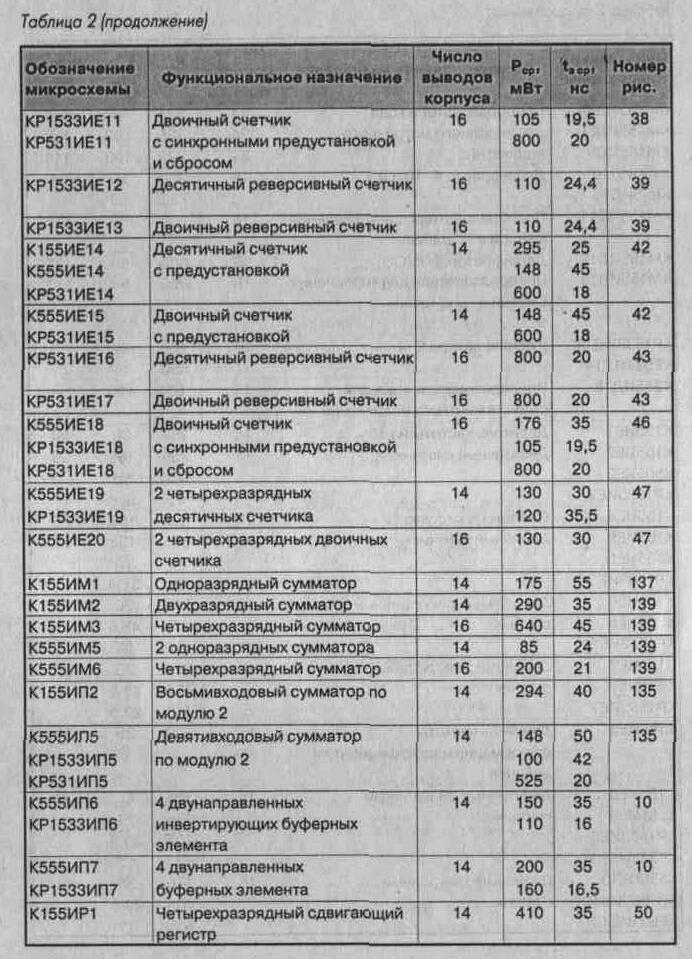

Таблица 2. Обозначение и технические характеристики микросхем ТТЛ (продолжение 2)

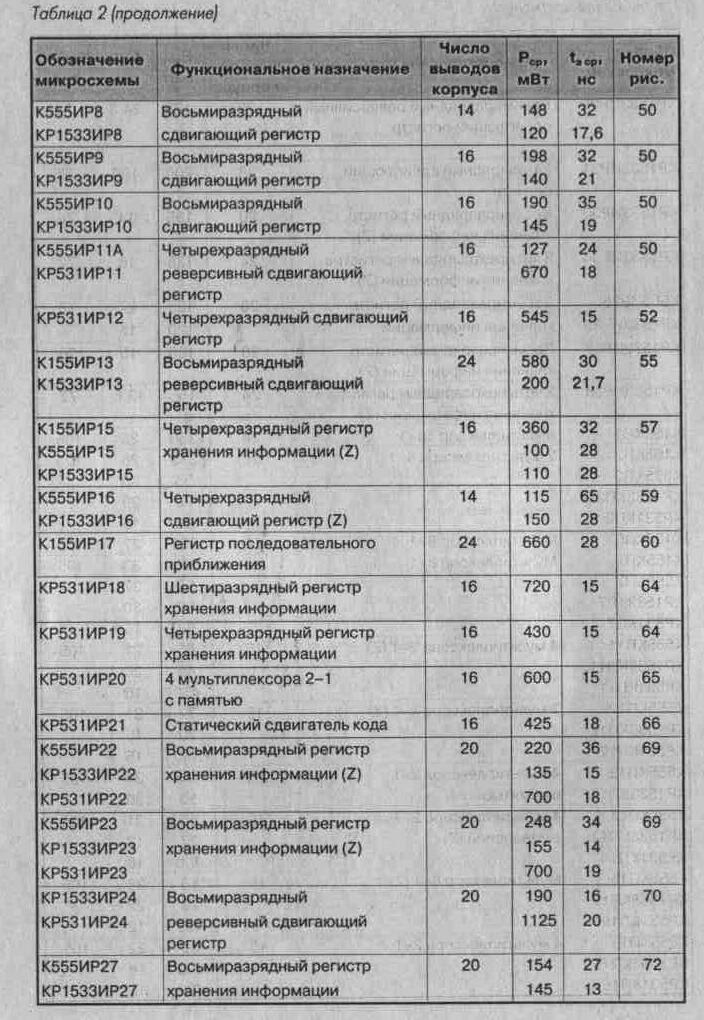

Таблица 2. Обозначение и технические характеристики микросхем ТТЛ (продолжение 3)

Таблица 2. Обозначение и технические характеристики микросхем ТТЛ (продолжение 4)

Таблица 2. Обозначение и технические характеристики микросхем ТТЛ (продолжение 5)

Таблица 2. Обозначение и технические характеристики микросхем ТТЛ (продолжение 6)

Таблица 2. Обозначение и технические характеристики микросхем ТТЛ (продолжение 7)

Таблица 2. Обозначение и технические характеристики микросхем ТТЛ (продолжение 8)

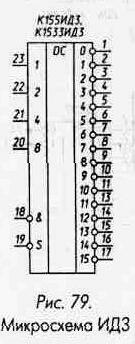

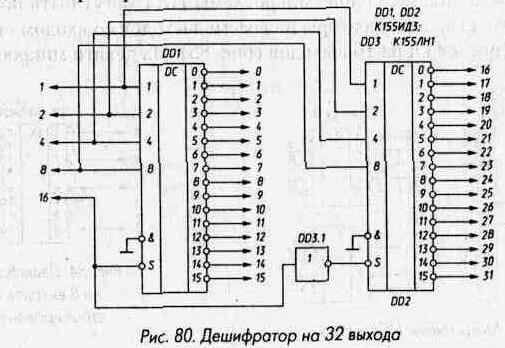

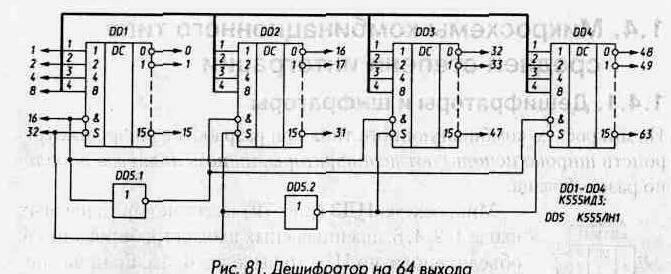

Таблица 2. Обозначение и технические характеристики микросхем ТТЛ

Таблица 3. Выводы питания микросхем ТТЛ

1.2 Микросхемы комбинационного типа малой степени интеграции.

1.2. Микросхемы комбинационного типа малой степени интеграции

Существует много типов микросхем ТТЛ малой степени интеграции, различающихся по функциональному назначению, нагрузочной способности, схеме выходного каскада. Работа логических элементов этих микросхем достаточно проста. Для элементов И выходной уровень лог. 1 формируется при подаче на все входы элемента уровней лог. 1, для элемента ИЛИ для формирования уровня лог. 1 на выходе достаточно подачи хотя бы на один вход уровня лог. 1. Элементы И-НЕ (основной элемент серий ТТЛ) и ИЛИ-НЕ дополнительно инвертируют выходной сигнал, элемент И-ИЛИ-НЕ состоит из нескольких элементов И, выходы которых подключены к входам элемента ИЛИ-НЕ.

По нагрузочной способности микросхемы можно разделить на стандартные (№10 для серий К 155 и КР531 и N = 20 и 40 для микросхем серий К555 и КР1533 соответственно), микросхемы с повышенной нагрузочной способностью (N = 30 и более), микросхемы со специальным выходным каскадом, обеспечивающим значительно более высокую нагрузочную способность в одном из логических состояний. Некоторые типы микросхем выпускают с так называемым «открытым» коллекторным выходом.

Отдельно следует отметить специальный класс микросхем с третьим состоянием выходного каскада, называемым также еще «высокоимпедансным», или «Z-состоянием», при котором микросхема отключается по своему выходу от нагрузки. Это, как правило, буферные элементы с относительно большой нагрузочной способностью.

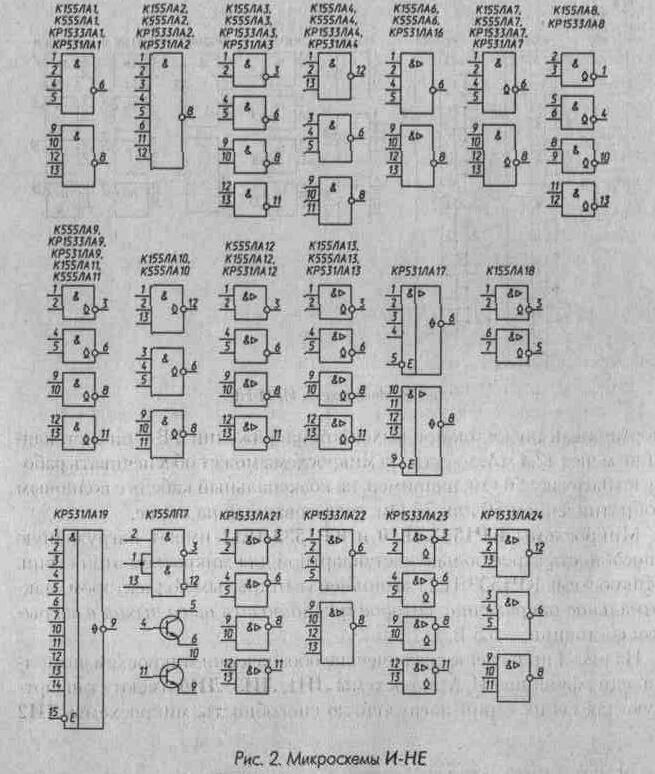

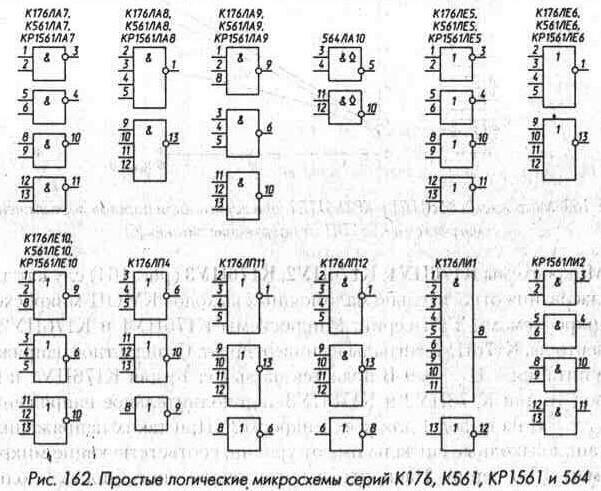

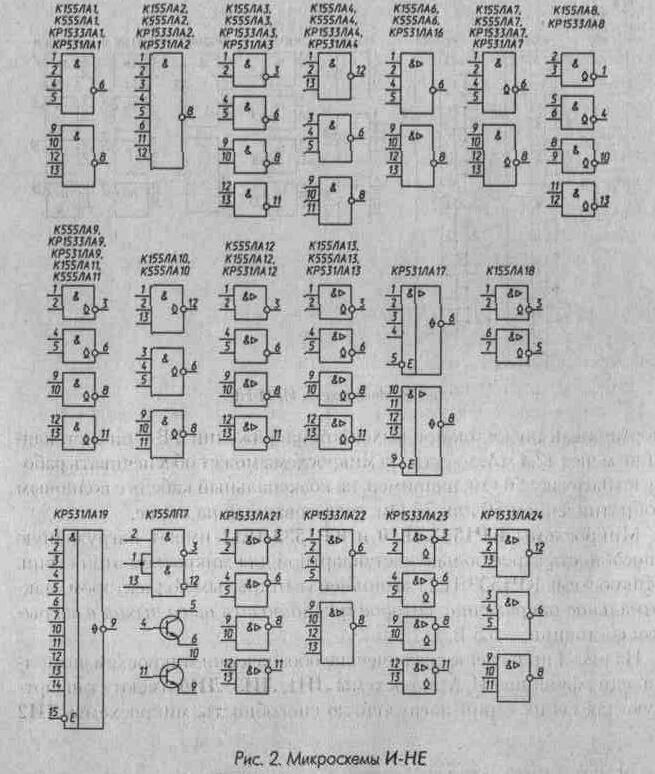

На рис. 2 приведены графические обозначения микросхем ТТЛ, выполняющих функции И-НЕ - самой многочисленной группы простых логических микросхем.

МикросхемыЛА1 -ЛА4 имеют стандартную для своей серии нагрузочную способность, микросхемыЛА6 иЛА12 всех серий, КР1533ЛА21 - КР1533ЛА24 - втрое большую (здесь и далее в тексте в названии оставлена только та его часть, которая определяет тип триггера, счетчика, логического элемента и т. п., если такие же обозначения используются в микросхемах нескольких серий).

МикросхемыЛА7 - ЛА11,ЛА13, КР1533ЛА23 выполнены с открытым коллектором, нагрузочная способность для ЛА7- ЛА11 в состоянии лог. 0 стандартная, для ЛА13 и КР1533ЛА23 - втрое большая. Максимально допустимое напряжение, которое можно подавать

на выход микросхемы ЛА11, находящейся в состоянии лог. 1, - 12 В, для остальных - 5,5 В.

МикросхемаКР531ЛА16 (рис. 2) - два мощных магистральных усилителя, выполняющих функцию 4И-НЕ. Нагрузочная способность каждого усилителя 60 мА в состоянии лог. 0 и 40 мА в состоянии лог. 1 при выходном напряжении 2 В, что позволяет работать на линию связи с волновым сопротивлением 50 Ом, нагруженную на конце. Кроме того, гарантируется, что при выходном напряжении 2,7 В в состоянии лог. 1 выходной ток составляет не менее 3 мА.

МикросхемаКР531ЛА17 (рис. 2) - два элемента 4И-НЕ с возможностью перевода выхода в высокоимпедансное состояние при подаче на вход Е лог. 1. При подаче на вход Е лог. 0 выходы активны, допустимые выходные токи составляют 50 мА в состоянии лог. 0 и 32 мА в состоянии лог. 1 при выходном напряжении 2 В, что обеспечивает возможность работы на линию связи с волновым сопротивлением 75 Ом. Дополнительно гарантируется, что при выходном напряжении 2,7 В в состоянии лог. 1 выходной ток составляет не менее 3 мА.

Входные токи микросхем КР531ЛА12, КР531ЛА13, КР531ЛА16, КР531ЛА17 по сигнальным входам в состоянии лог. 0-4 мА, по входам Е - 2 мА.

Микросхема К155ЛА18 (рис. 2) выполнена с открытым коллектором, ее выходное напряжение в состоянии лог. 0 не более 0,5 В при выходном втекающем токе 100 мА и не более 0,8 В при токе 300 мА. Максимальное напряжение на выходе в состоянии лог. 1 — 30 В, что позволяет коммутировать нагрузку мощностью до 9 Вт - электромагнитные реле, маломощные электродвигатели. Лампы накаливания, однако, можно использовать на номинальный ток не более 60 мА, так как сопротивление нити лампы в холодном состоянии значительно меньше номинального.

МикросхемаКР531ЛА19(рис. 2) - двенадцативходовый элемент И-НЕ с возможностью перевода выхода в высокоимпедансное состояние при подаче лог. 1 на вход Е. В состоянии лог. 1 при выходном напряжении 2,4 В микросхема допускает выходной ток до 6,5 мА, в состоянии лог. 0-20 мА.

Микросхема К155ЛП7 (рис. 2) - два стандартных логических элемента И-НЕ с двумя объединенными входами и два n-р-n транзистора с предельно допустимым коллекторным напряжением 30 В и максимальным током коллектора 300 мА. Подложка микросхемы подключена к выводу 8, что позволяет, подключив ее к источнику отрицательного напряжения, коммутировать транзистором и отрицательные сигналы, не выходящие по амплитуде за напряжение этого источника.

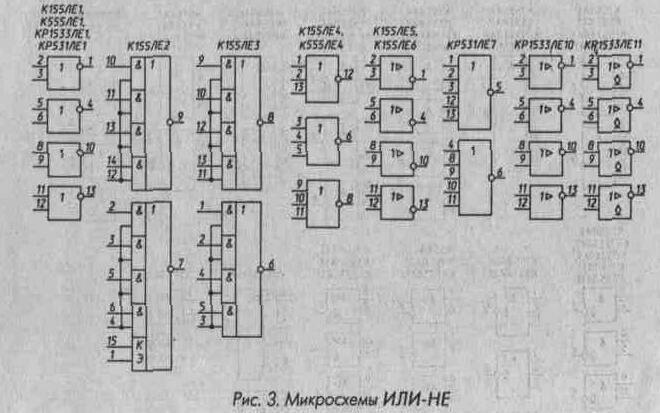

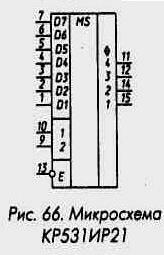

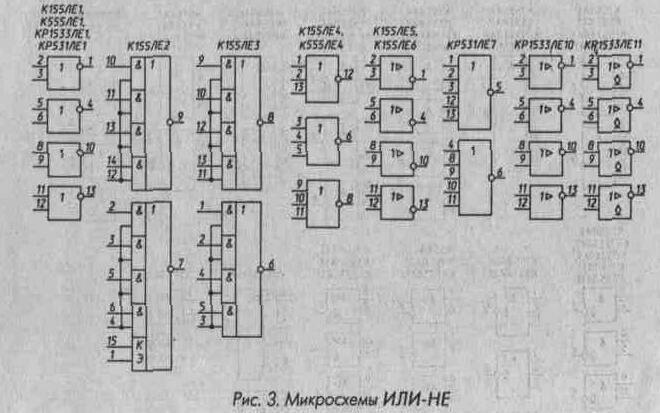

На рис. 3 приведены графические обозначения микросхем, выполняющих функцию ИЛИ-НЕ. На входах микросхемК155ЛЕ2, К155ЛЕЗ установлены дополнительные элементы И, позволяющие стробировать входные сигналы. Нагрузочная способность микросхем ЛЕ1 - ЛЕ4, КР531ЛЕ7 стандартная для соответствующей серии, микросхемК155ЛЕ5иК155ЛЕ6 в состоянии лог. 0-48 мА, что соответствует N = 30, в состоянии лог. 1 - выше. Микросхема К155ЛЕ5 может обеспечить при выходном напряжении 2,4 В вытекающий ток 2,4 мА, микросхема К155ЛЕ6 - 13,2 мА. Для микросхемы К155ЛЕ6

нормирован также ток при выходном напряжении 2 В - он составляет не менее 42,4 мА, то есть эта микросхема может обеспечивать работу на нагрузку 50 Ом, например, на коаксиальный кабель с волновым сопротивлением 50 или 75 Ом, согласованный на конце.

МикросхемыКР1533ЛЕ10и КР1533ЛЕ11 имеют нагрузочную способность втрое большую стандартной для микросхем этой серии. Микросхема КР1533ЛЕ11 выполнена с открытым коллектором, максимальное напряжение, которое можно подать на ее выход в закрытом состоянии, - 5,5 В.

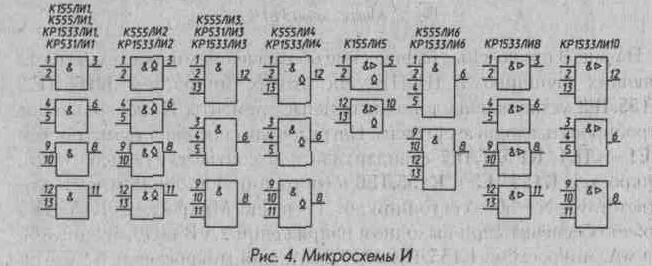

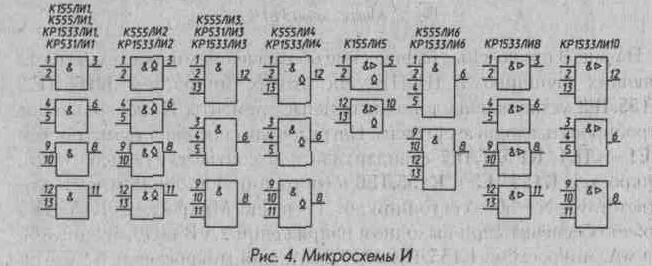

На рис. 4 приведены графические обозначения микросхем, выполняющих функцию И. МикросхемыЛИ1, ЛИЗ, ЛИ6 имеют стандартную для своих серий нагрузочную способность, микросхемыЛИ2

и ЛИ4 выполнены с открытым коллектором, их нагрузочная способность в состоянии лог. 0 стандартная, в состоянии лог. 1 допускается подача напряжения 5,5 В.

МикросхемаК155ЛИ5 выполнена с открытым коллектором, ее нагрузочная способность такая же, как у К155ЛА18.

МикросхемыКР1533ЛИ8 и КР1533ЛИ10

имеют нагрузочную способность втрое большую стандартной для микросхем этой серии.

На рис. 5 приведены графические обозначения микросхем, выполняющих функцию ИЛИ. Микросхема ЛЛ1 имеет стандартную нагрузочную способность, микросхема К155ЛЛ2 выполнена с открытым коллектором и имеет нагрузочную способность такую же, как К155ЛА18.

МикросхемаКР1533ЛЛ4 имеет нагрузоч ную способность втрое большую стандартной для микросхем этой серии

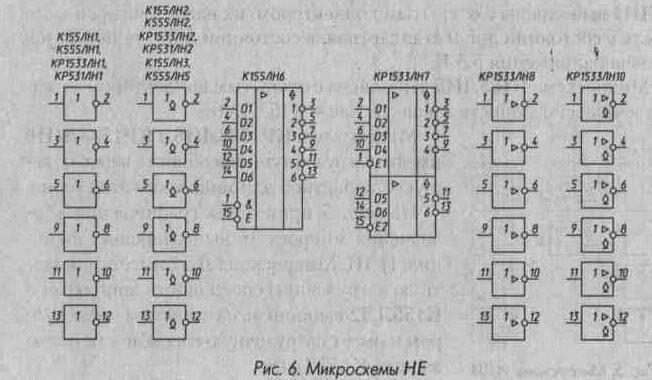

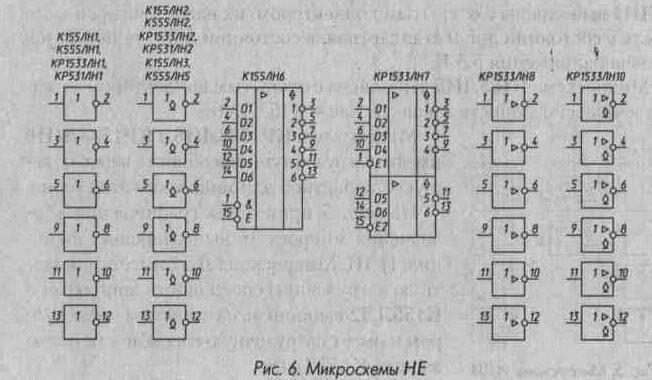

На рис. 6 приведены графические обозначения микросхем, выполняющих функцию НЕ (инверторы). МикросхемыЛН1 имеют стандартную нагрузочную способность, аЛН2, К155ЛНЗ, К155ЛН5 выполнены с открытым коллектором и имеют стандартную нагрузочную способность в состоянии лог. 0. Для К155ЛНЗ и К155ЛН5 дополнительно гарантируется, что при втекающем токе 40 мА выходное напряжение в состоянии лог. 0 не превышает 0,7 В. Допустимое напряжение на выходе микросхемы в состоянии лог. 1 составляет 5,5, 30 и 15 В для ЛН2, К155ЛНЗ и К155ЛН5 соответственно.

МикросхемаК155ЛН6 (рис. 6) - шесть мощных инверторов с возможностью перевода выходов в высокоимпедансное состояние. Управление состоянием выходов производится по двум равноправным входам управления Е (1 и 15), собранным по схеме, выполняющей функцию И. При подаче на оба указанных входа лог. 0 выходы инверторов переходят в активное состояние и инвертируют входные сигналы, при подаче хотя бы на один вход лог. 1 - переходят в высокоимпедансное состояние.

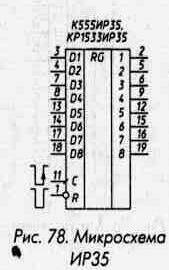

Нагрузочная способность инверторов довольно велика - при лог. 0 на выходе выходной втекающий ток может достигать 32 мА, при этом выходное напряжение не более 0,4 В, при лог. 1 на выходе выходной вытекающий ток - до 5,2 мА при выходном напряжении 2,4 В.

МикросхемаКР1533ЛН7 (рис. 6) - шесть инверторов с повышенной нагрузочной способностью и возможностью перевода выходов в высокоимпедансное состояние. Инверторы объединены в две группы,

у каждой из которых свой вход управления. Подача лог. 0 на вход Е1 включает инверторы с выходами 1-4, на вход Е2 - с выходами 5 и 6. Нагрузочная способность микросхемы 12 мА при 0,4 В в состоянии лог. 0 и 3 мА при 2,4 В в состоянии лог. 1.

МикросхемаКР1533ЛН8 (рис. 6) - шесть инверторов с повышенной нагрузочной способностью; максимальный уровень в состоянии лог. 0 -0,4 В при втекающем токе 12 мА и 0,5 В при 24 мА, минимальный уровень в состоянии лог. 1 2,4 В при вытекающем токе 3,0 мА и 2,5 В при 0,4 мА.

МикросхемаКР1533ЛН10 имеет нагрузочную способность втрое большую стандартной для микросхем этой серии. Микросхема выполнена с открытым коллектором, максимальное напряжение, которое можно подать на ее выход в закрытом состоянии - 5,5 В.

На рис. 7 приведены графические обозначения микросхем, выполняющих функцию И-ИЛИ-НЕ и расширителей И-ИЛИ. Все микросхемы И-ИЛИ-НЕ имеют стандартные выходы, кромеКР531ЛР10, которая выполнена с открытым коллектором, допустимое напряжение для нее в состоянии лог. 1 - 5,5 В. Следует отметить различие микросхемК155ЛР4 и К555ЛР4, КР1533ЛР4, а такжеК555ЛР11, КР1533ЛР11 и КР531ЛР11. МикросхемыК155ЛР1, К155ЛРЗ, К155ЛР4 имеют входы для подключения расширителей И-ИЛИ К155ЛД1 и К155ЛД2, увеличивающих число групп И в функции ИЛИ этих микросхем. Аналогичные входы для расширения числа входов по ИЛИ имеет микросхемаК155ЛЕ2.

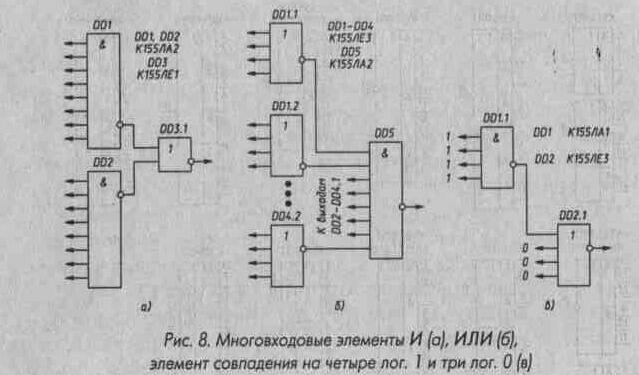

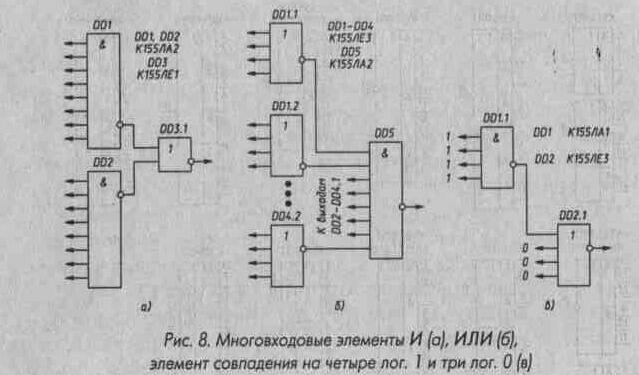

Однако более простой способ построения элементов И или ИЛИ с большим числом входов - каскадное соединение микросхем,

выполняющих функции И-НЕ и ИЛИ-НЕ. На рис. 8 (а) приведена схема элемента И на 16 входов, на рис. 8 (б) - элемента ИЛИ на 32 входа. На рис. 8 (в) приведена схема элемента совпадения, формирующего на своем выходе лог. 1 при лог. 1 на четырех верхних по схеме входах и лог. 0 на трех нижних. Такой элемент может использоваться для дешифрации определенных состояний счетчиков и других устройств.

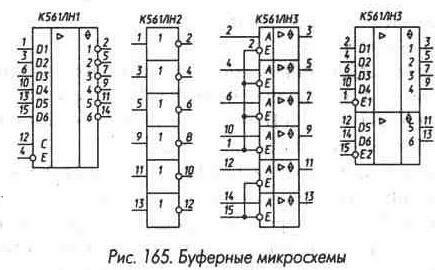

На рис. 9 приведены графические обозначения микросхем - повторителей входного сигнала.

МикросхемаЛП8 - четыре повторителя входного сигнала с высокоимпедансным состоянием. При лог. 0 на управляющем входе Е сигналы с входа D элемента проходят на выход элемента без инверсии. При лог. 1 на входе Е выход элемента переходит в высокоимпедансное состояние. При лог. 0 на выходе микросхема К155ЛП8 обеспечивает втекающий ток 16 мА, при лог. 1 - вытекающий 5,2 мА, К555ЛП8 - 24 мА и 2,6 мА соответственно.

МикросхемаК155ЛП9 (рис. 9) - шесть повторителей входного сигнала с открытым коллектором, ее выходные параметры такие же, как и у К155ЛНЗ.

МикросхемаК155ЛП10 (рис. 9) - шесть мощных повторителей с возможностью перевода выходов в высокоимпедансное состояние.

Логика управления и нагрузочная способность этой микросхемы такие же, как и у К155ЛН6.

МикросхемаК155ЛП11 (рис. 9) - шесть мощных повторителей, подобных повторителям микросхемы К155ЛП10, но разбитых на две группы, каждая из которых имеет свой вход управления. Подача лог. 0 на вход Е1 включает повторители с выходами 1-4, вход Е2 управляет выходами 5 и 6. Нагрузочная способность микросхемы К155ЛП11 такая же, как у К155ЛН6.

МикросхемыКР1533ЛП16 и КР1533ЛП17 имеют нагрузочную способность втрое большую стандартной для микросхем этой серии. Микросхема КР1533ЛП17 выполнена с открытым коллектором,

максимальное напряжение, которое можно подать на ее выход в закрытом состоянии - 5,5 В.

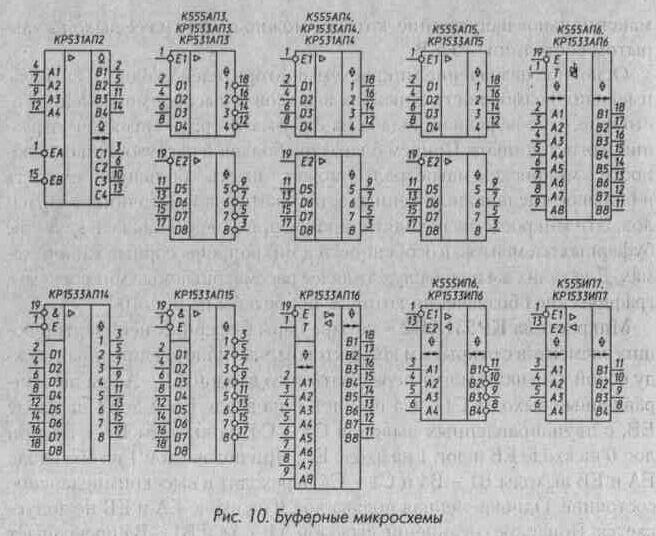

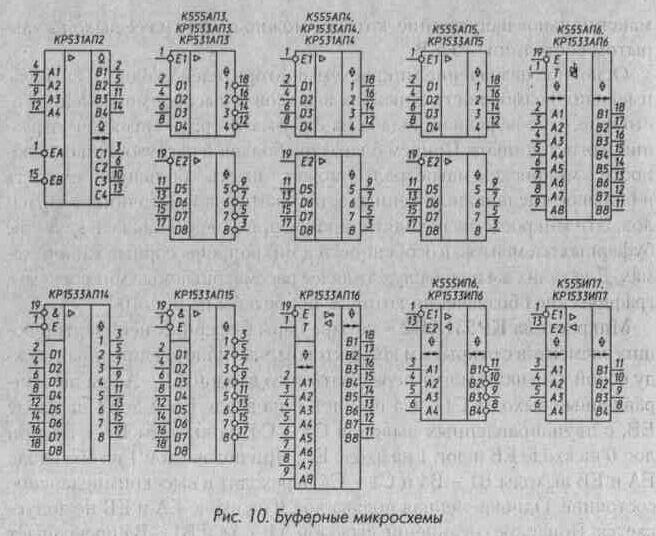

Основное назначение микросхем-повторителей входного сигнала, имеющих возможность перевода выходов в высокоимпедансное состояние, - поочередная подача на одну магистраль сигналов от различных источников. Причем благодаря большой нагрузочной способности микросхем магистраль может иметь большую емкость и большое число подключенных к ней нагрузок и источников сигналов. Эти микросхемы находят широкое применение также в качестве буферных элементов, в особенности в микропроцессорных микросхемах. Для таких же целей служат далее рассматриваемые микросхемы, графические обозначения которых приведены на рис. 10.

МикросхемаКР531АП2 - четыре пары буферных неинвертирующих элементов с открытым коллектором, частично соединенных между собой. Сигналы могут передаваться со входов А1 - А4 на двунаправленные выходы С1 - С4 при лог. 0 на входе ЕА и лог 1 на входе ЕВ, с двунаправленных выводов С1 - С4 на выходы В1 - В4 при лог. 0 на входе ЕВ и лог. 1 на входе ЕА. При подаче лог. 1 на оба входа ЕА и ЕВ выходы В1 - В4 и С1 - С4 переходят в высокоимпедансное состояние. Одновременная подача лог. 0 на входе ЕА и ЕВ не допускается. Попарное соединение выводов А1 - А4 и В1 - В4 превращает микросхему в четыре двунаправленных ключа, максимальный выходной ток в состоянии лог. 0-60 мА, максимальные входное и выходное напряжения в состоянии лог. 1-10,5 В, входной ток в состоянии лог. 0 не превышает 0,15 мА.

МикросхемаАПЗ (рис. 10) - восемь инвертирующих буферных элементов с повышенной нагрузочной способностью и возможностью перевода выходов в высокоимпедансное состояние. Элементы разбиты на две группы по четыре, у каждой из групп свой вход управления для включения элементов и их перевода в третье состояние (Е1 и Е2). Включение элементов каждой группы происходит при подаче на соответствующий вход (Е1 и Е2) лог. О, переход в высокоимпедансное состояние - при подаче лог. 1. Выходной втекающий ток микросхемы К555АПЗ в состоянии лог. О при напряжении на выходе 0,5 В может достигать 24 мА, вытекающий в состоянии лог. 1 при напряжении на выходе 2 В - 15 мА. Для микросхем КР1533АПЗ максимальный уровень лог. 0 0,4 В при втекающем токе 12 мА и 0,5 В при 24 мА. Минимальный уровень лог. 1 2,4 В при вытекающем токе 3 мА и 2,5 В при 0,4 мА. Нагрузочная способность микросхемы КР531АПЗ в состоянии лог. 0 64 мА, в состоянии лог. 1 3 мА при выходном

напряжении 2,4 В и 15 мА при 2 В. Входные токи по сигнальным входам D1 - D8 в состоянии лог. 0 0,4 мА.

МикросхемаАП4 (рис. 10) - восемь аналогичных буферных элементов без инверсии. Отличие ее в том, что один из входов включения элементов и их перевода в третье состояние (El) - инверсный, подобно АПЗ, второй (Е2) - прямой. Нагрузочная способность этой микросхемы такая же, как у АПЗ.

МикросхемаАП5 (рис. 10) - восемь неинвертирующих буферных элементов, обе группы которых имеют инверсные входы управления включением. В остальном эта микросхема аналогична АП4.

Микросхемы АПЗ - АП5 служат для буферизации и коммутации сигналов в микропроцессорных устройствах, например, сигналов адреса, сигналов управления при организации внутренних и внешних шин микро-ЭВМ. Основное их назначение - обеспечение однонаправленной передачи информации. Однако при необходимости с их помощью можно обеспечить и двунаправленную передачу. На рис. 11 в качестве примера показано соединение выводов микросхемы АП4 для получения двунаправленного буферного элемента. При подаче лог. 0 на объединенные между собой входы Е1 и Е2 происходит передача сигнала

от расположенных слева по рисунку выводов микросхемы (входы А1 -А4) к правым (В1 - В4), при подаче лог. 1 - наоборот: от В1 - В4 к А1 -А4. Два треугольника в среднем поле графического обозначения микросхемы символизируют усиление и направление передачи сигнала, верхний - при подаче активного сигнала на вход Е1 (для инверсного входа - лог. 0), нижний - на вход Е2 (для прямого входа - лог. 1).

Интересно отметить, что расположение информационных входов и выходов микросхем АПЗ - АП5 сделано специально такое, как показано на рис. 11, - для удобного их соединения.

Однако для организации двунаправленной передачи информации удобнее использовать специально предназначенные для этой цели микросхемы, описываемые далее.

Микросхема АП6 (см. рис. 10) - восемь двунаправленных неинвертирующих буферных элементов. Кроме двух групп информационных выводов А1 - А8 и В1 - В8, микросхема имеет два входа управления - Е и Т. Сигнал лог. 0, подаваемый на

вход Е, разрешает включение буферных элементов, лог. 1 - переводит все выводы микросхемы в Z-состояние. Сигнал на входе Т действует при лог. 0 на входе Е и определяет направление передачи сигналов - при лог. 1 на входе Т выводы А1 - А8 являются входами, В1 - В8 - выходами, при лог. 0 - наоборот; В1 - В8 - входы, А1 - А8 - выходы. Два треугольника у входа Т символизируют усиление и направление распространения сигнала, верхний - при лог. 1 на входе Т, нижний - при лог. 0.

Микросхема АП6 по своему функционированию (но, к сожалению, не по разводке выводов) соответствует микросхеме КР580ВА86, но потребляет в 1,7 раза меньшую мощность (К555АП6).

МикросхемаКР1533АП14 (рис. 10) содержит восемь однонаправленных буферных элементов с возможностью перевода их выходов в высокоимпедансное состояние. При подаче на оба входа разрешения Е лог. 0 выходы микросхемы переходят в активное состояние и на них появляются без инверсии сигналы с соответствующих входов D1 - D8. При поступлении на любой из входов Е лог. 1 выходы переходят в высокоимпедансное состояние. Микросхема КР1533АП15 (рис. 10) аналогична микросхеме КР1533АП14, только она инвертирует входные сигналы.

МикросхемаКР1533АП16 (рис. 10) состоит из восьми двунаправленных буферных элементов и, в основном, аналогична микросхеме

КР1533АП6. Она инвертирует сигналы при передаче их с выводов А на выводы В и не инвертирует их при передаче в обратном направлении. На графическом изображении микросхемы КР1533АП16 для отражения этого свойства у вывода Т, определяющего направление передачи информации, верхний треугольник, символизирующий передачу сигналов с выводов А на выводы В при подаче на вход Т лог. 1, дополнен кружком инверсии, а нижний треугольник (на входе Т - лог. 0) показан без такого кружка.

МикросхемаИП6 (рис. 10) - четыре двунаправленных инвертирующих буферных элемента. Логика работы входов управления Е1 и Е2

следующая: при лог. 0 на обоих входах передача сигналов происходит от выводов А1 - А4 к выводам В1 - В4, при лог. 1 на обоих входах - от выводов В1 - В4 к А1 - А4. При лог. 1 на входе Е1 и лог. 0 на входе Е2 все информационные выводы микросхемы переходят в Z-состояние, подача лог. 0 на вход Е1 и лог. 1 на вход Е2 одновременно недопустима. Треугольники на графическом обозначении микросхемы и входов Е1 и Е2 символизируют усиление и направление распространения информации при подаче активных сигналов на эти входы.

Нагрузочная способность микросхемы ИП6 такая же, как у АПЗ.

МикросхемаИП7 отличается от ИП6 только тем, что не инвертирует сигналы.

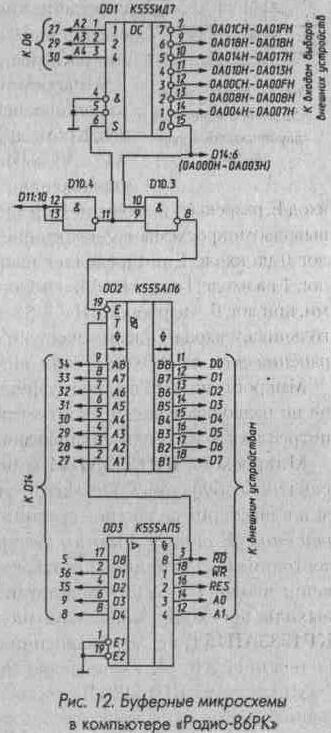

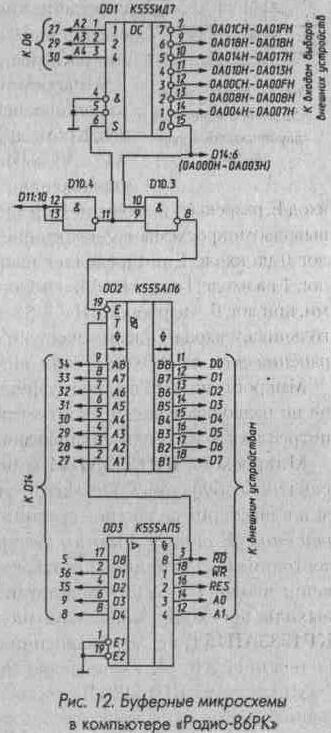

На рис. 12 в качестве примера показано использование буферных микросхем для подключения внешних устройств к компьютеру «Радио-86РК». Если из всех внешних устройств ограничиться лишь таймером КР580ВИ53, его вполне можно смонтировать на

плате компьютера без буферных элементов. Если же предполагается подключение нескольких внешних устройств (таймер, часы, АЦПУ, модем и др.), из-за малой нагрузочной способности центрального процессора КР580ВМ80 необходимы буферные элементы.

На рис. 12 микросхема DD3 обеспечивает буферизацию управляющих сигналов RD, WR, RES и двух младших адресов АО и А1. Микросхема DD2 буферизирует двунаправленную шину данных. Включение этой микросхемы по входу Е должно происходить лишь при обращении к внешним устройствам, что обеспечивается микросхемой DD1 и элементами D10.4 и D10.3.

В основном варианте компьютера «Радио-86РК» адреса А000Н -BFFFH использованы для микросхемы D14. Практически используются только четыре адреса - А000Н, А001Н, А002Н, А00ЗН. Установкой дешифратора DD1 можно обеспечить при сохранении этих адресов для D14 использование следующих четырех адресов А004Н, АООЗН, А006Н, А007Н - для первого внешнего устройства, например таймера;

следующих четырех А00ЗН - А00ВН - для второго; следующих четырех А00СН - A00FH - для третьего и т. д., всего можно будет подключить семь дополнительных внешних устройств, для каждого из которых будет отведено четыре адреса. Если входы 1,2,4 дешифратора DD1 подключить к другим выходам адреса микропроцессора D6, например, А10, All, A12, на каждое внешнее устройство будет отведено по 1024 адреса.

Элементы D10.4 и D10.3 необходимы для выключения DD2 при обращении микропроцессора к D14, то есть по адресам А000Н - А00ЗН. В этом случае лог. 0 с выхода О DD1 включает D10.3 и лог. 1 с его выхода выключает DD2. Направление передачи сигнала через DD2 определяется сигналом RD. При чтении из внешнего устройства сигнал RD

принимает значение лог. 0 и происходит передача сигналов через DD2 от внешнего устройства к микропроцессору, в остальных случаях - от микропроцессора к внешнему устройству.

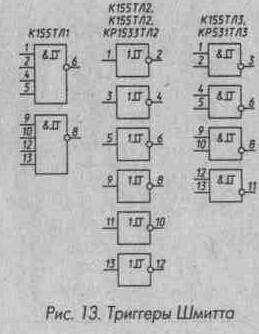

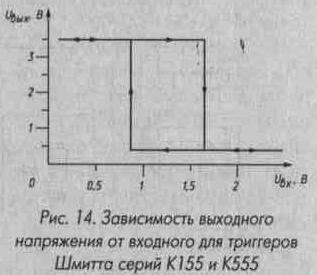

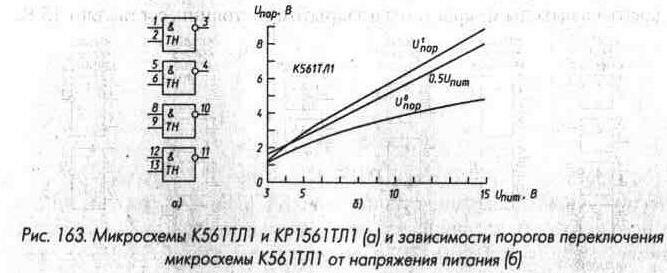

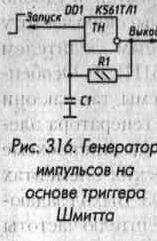

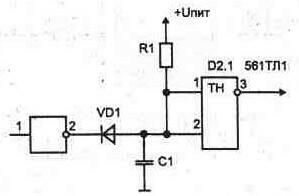

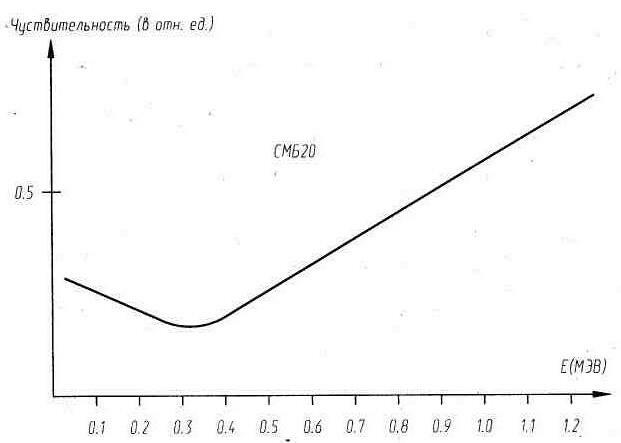

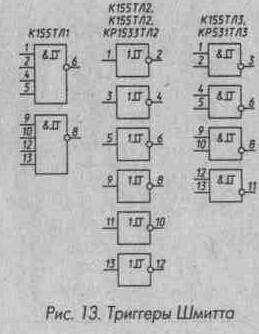

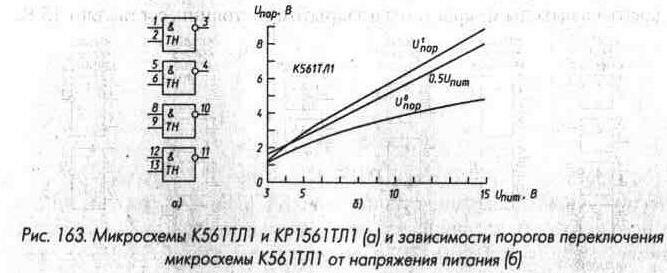

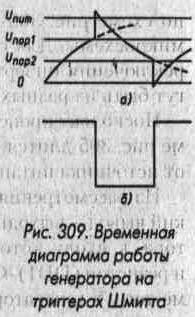

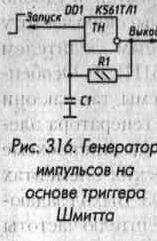

На рис. 13 приведены микросхемы -инвертирующие триггеры Шмитта. Микросхема К155ТЛ1 - два четырехвходовых элемента И-НЕ, микросхемаТЛЗ - четыре двухвходовых, микросхемаТЛ2 - шесть инверторов.

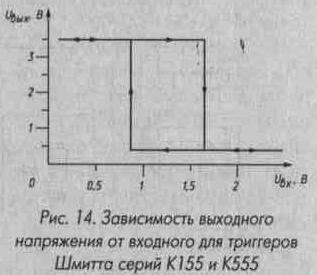

Указанные микросхемы при плавном изменении входного сигнала обеспечивают

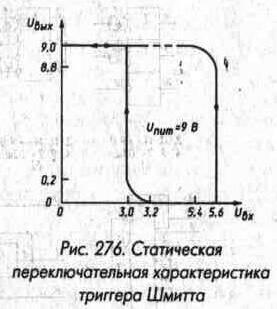

скачкообразное переключение выходного (рис. 14). При повышении напряжения на входе элемента микросхемы от нуля выходное напряжение скачком изменяется с лог. 1 на лог. 0 при напряжении на входе около 1,65 В. При снижении напряжения на входе обратное изменение выходного напряжения происходит при напряжении на входе около 0,85 В для триггеров Шмитта серий К155 и К555ТЛ2 и около 1,2 В для КР531ТЛЗ.

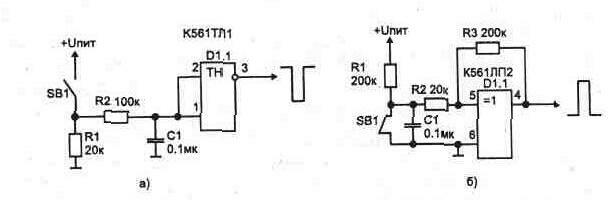

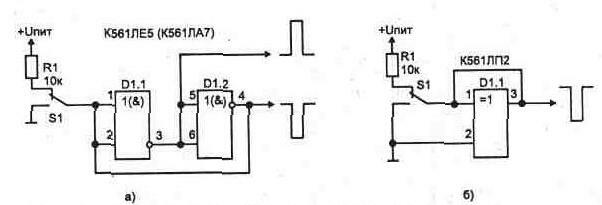

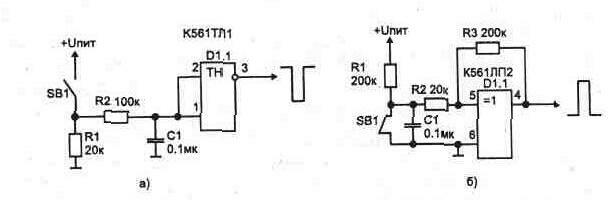

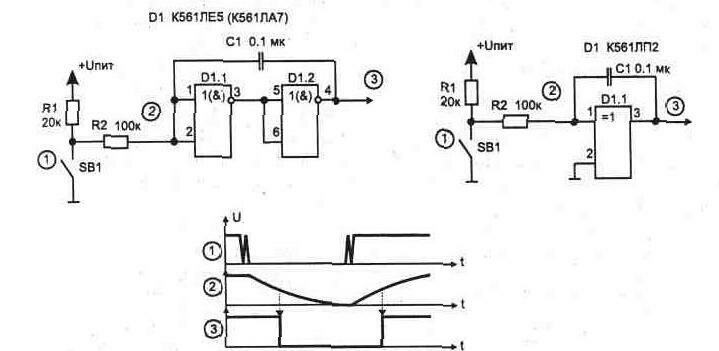

Триггеры Шмитта применяют для формирования ТТЛ-сигнала из синусоидального, для приема сигналов при большом уровне помех, в формирователях и генераторах импульсов и в других случаях.

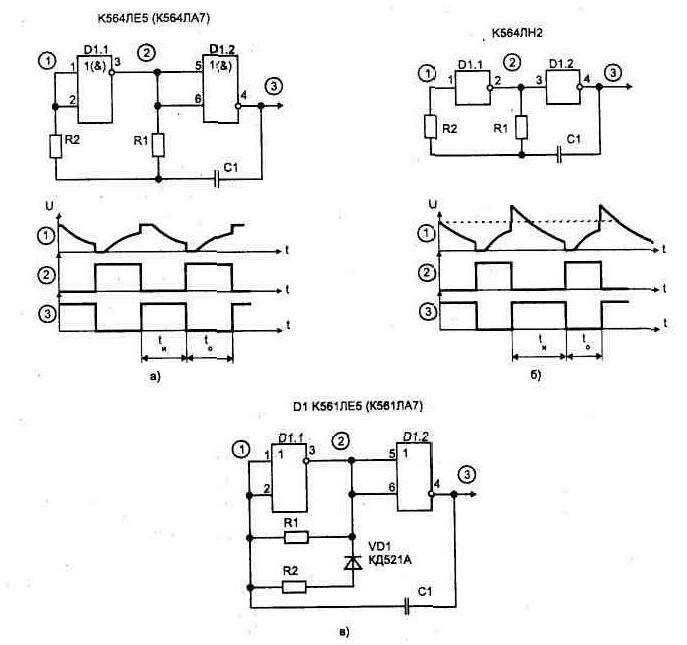

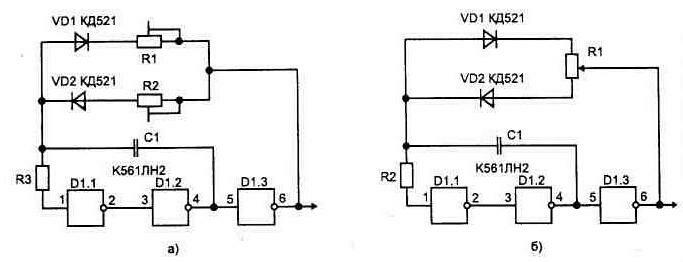

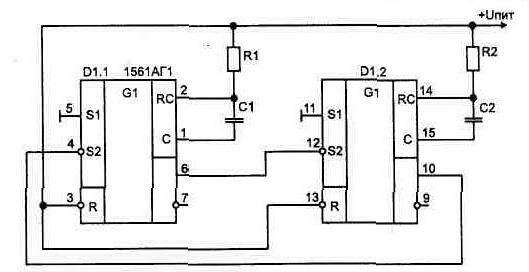

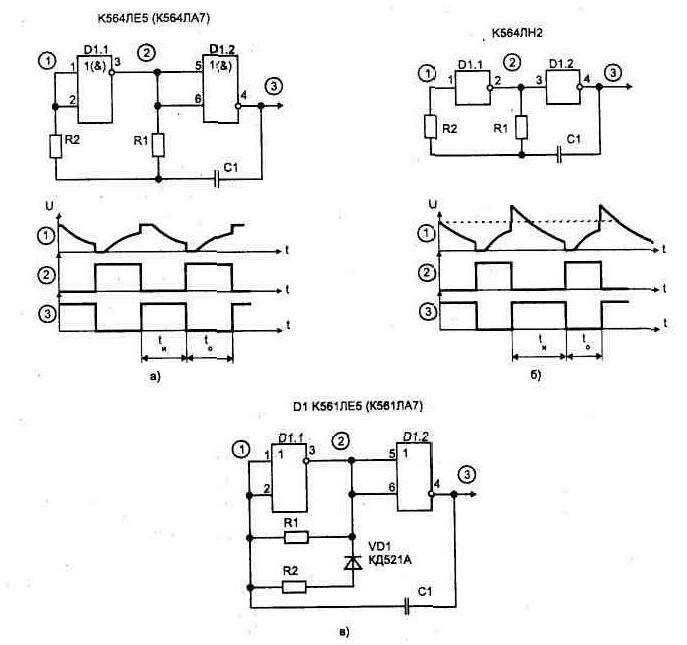

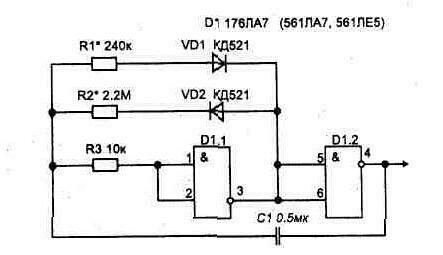

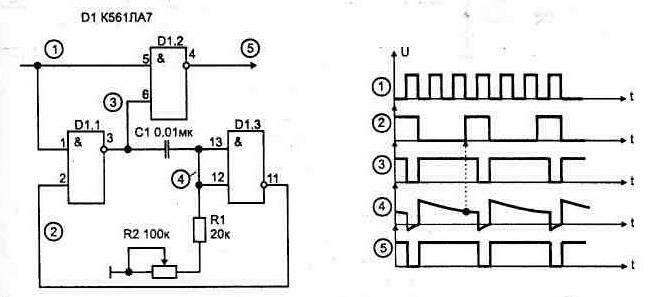

На рис. 15, а показана схема формирователя импульса сброса при включении питания, обеспечивающего крутой фронт при большой длительности импульса, на рис. 15, б - простейшего генератора импульсов.

Изучение работы более сложных микросхем удобно продолжить с микросхем последовательностного типа.

Рис. 10 Буферные микросхемы

Рис. 11 Микросхема К555АП4 в качестве двунаправленного буфера

Рис. 12 Буферные микросхемыв компьютере "Радио-86РК"

Рис. 13 Триггеры Шмидта

Рис. 14 Зависимость выходного напряжения от входного для триггеров Шмидта серий К155 и К555

Рис. 15 Формирователь импульса начальной установки и генератор импульсов на триггере Шмидта

Рис. 2 Микросхемы 2И-НЕ

Рис. 3 Микросхемы ИЛИ-НЕ

Рис. 4 Микросхемы И

Рис. 5 Микросхемы ИЛИ

Рис. 6 Микросхемы НЕ

Рис. 7 Микросхемы И-ИЛИ-НЕ и расширители И-ИЛИ

Рис. 8 Многовходовые элементы И (а), ИЛИ (б), элементы совпадения на четыре лог. 1 и три лог. 0

Рис. 9 Микросхемы повторителей

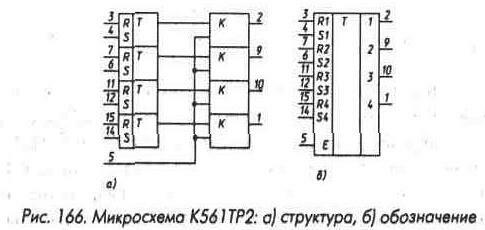

1.3 Микросхемы последовательстного типа.

1.3. Микросхемы последовательностного типа

Микросхемы последовательностного типа, как уже указывалось, характеризуются наличием памяти. Запись информации в ячейки памяти этих микросхем или изменение содержащейся в них информации производится импульсами. Входы микросхем для подачи импульсов записи могут быть статическими или динамическими. Статические входы характеризуются тем, что импульс, поданный на этот вход, действует в течение всего времени, пока он подан. Как правило, это входы сброса

триггеров, счетчиков и регистров, входы, стробирующие предварительную установку.

Для динамических входов характерно срабатывание по фронту, то есть микросхема чувствительна не к самому импульсу в течение всего времени, пока он подан, а лишь к его фронту или спаду. Точнее, запись (изменение) информации происходит только в моменты смены сигнала на динамическом входе с лог. 1 на лог. 0 или с лог. 0 на лог. 1.

В большинстве случаев для динамических входов безразлично, подаются на вход импульсы положительной или отрицательной полярности (здесь и далее под импульсом отрицательной полярности понимается изменение сигнала с лог. 1 до лог. 0 с последующим изменением с лог. 0 на лог. 1), запись (изменение) информации происходит при изменении сигнала с лог. 1 на лог. 0 для одних типов микросхем, с лог. 0 на лог. 1 для других типов.

При разработке устройств следует придерживаться правила - все последовательностные микросхемы должны переключаться по спадам тактовых импульсов, поэтому при описании микросхем, имеющих динамические входы, указывается, что они срабатывают по спадам импульсов соответствующей полярности. На схемах включения микросхем для импульсов, подаваемых на динамические входы, стрелками отмечены спады импульсов, по которым срабатывают микросхемы, а на графических обозначениях микросхем на их динамических входах штрихом отмечено направление перепада, по которому происходит срабатывание.

1.3.1 Триггеры.

1.3.1. Триггеры

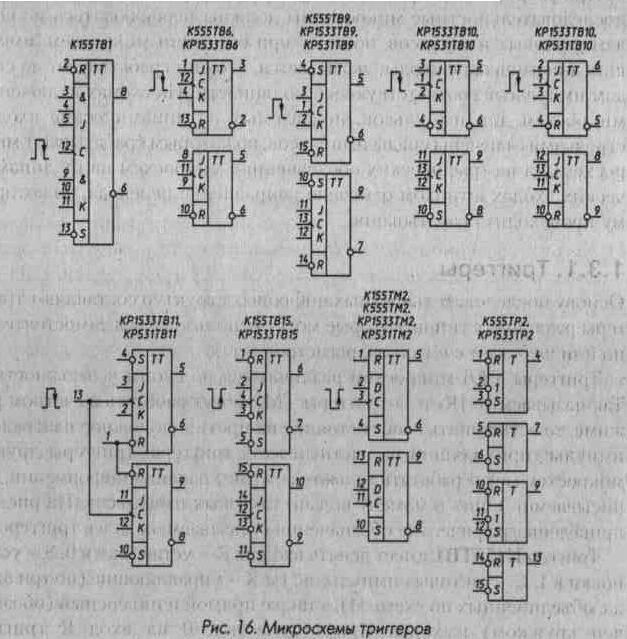

Основу последовательностных цифровых структур составляют триггеры различных типов, которые могут использоваться самостоятельно или в составе счетчиков, регистров и т. д.

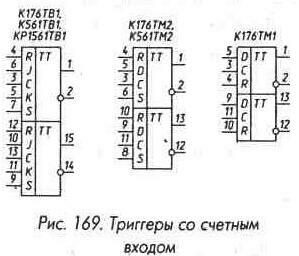

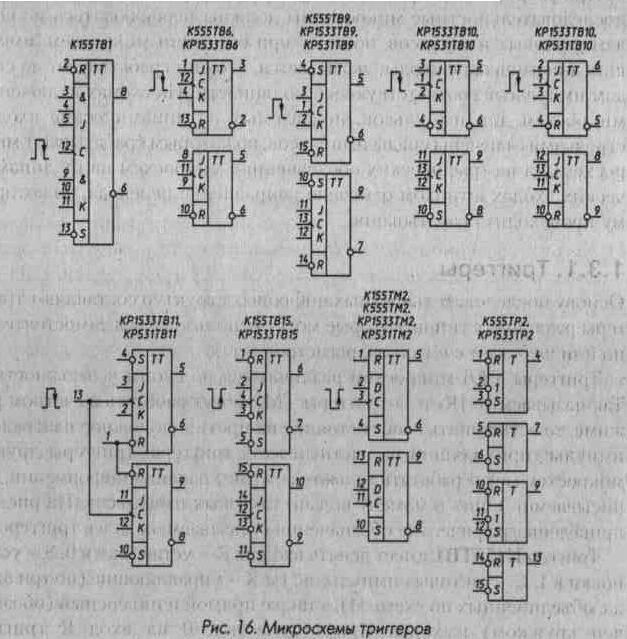

Триггеры ТТЛ-микросхем различаются по своим возможностям. Так называемые JK- и D-триггеры ТМ2 могут работать в счетном режиме, то есть менять свое состояние на противоположное на каждый импульс, приходящий на счетный вход триггера. Триггеры других микросхем могут работать только в режиме хранения информации, записываемой в них в момент подачи тактовых импульсов. На рис. 16 приведены графические обозначения описываемых далее триггеров.

ТриггерК155ТВ1 имеет девять входов: R - установки в 0, S - установки в 1, С - тактовых импульсов, J и К - управляющие (по три входа, объединенных по схеме И), а также прямой и инверсный (обозначен кружком) выходы. При подаче лог. 0 на вход R триггер

устанавливается в нулевое состояние, при котором на прямом выходе лог. 0, на инверсном - лог. 1. При подаче лог. 0 на вход S триггер устанавливается в единичное состояние. При подаче лог. 0 одновременно на оба входа (R и S) триггера на обоих выходах появляется лог. 1. Состояние триггера после снятия лог. 0 со входов R и S определяется тем, с какого из входов лог. 0 снят последним. Аналогично управляются по входам R и S все описываемые далее триггеры ТТЛ.

Сложнее происходит работа триггера при подаче сигналов на входы С, J и К. Наиболее простой режим - при лог. 1 на входах J и К. В этом случае JK-триггер работает, как обычный триггер со счетным входом: по спаду каждого положительного импульса на тактовом входе С состояние триггера меняется на противоположное. Если хотя бы на одном входе J и на одном входе К одновременно лог. 0, состояние триггера при подаче импульсов по тактовому входу С не меняется.

Если на всех входах J лог. 1, хотя бы на одном входе К - лог. 0, по спаду положительного импульса на входе С триггер устанавливается в единичное состояние независимо от своего предыдущего. Если хотя бы на одном входе J лог. 0, на всех входах К - 1, по спаду импульса на входе С триггер устанавливается в нулевое состояние.

Изменение сигналов на J- и К-входах при лог. 0 на входе С не влияет на состояние JK-триггера. Если же на входе С лог. 1, изменение сигналов на J- и К-входах само по себе не влияет на состояние выходов, но запоминается. Если триггер находится в нулевом состоянии и во время действия положительного тактового импульса на всех входах J была кратковременно лог. 1, по спаду импульса положительной полярности триггер перейдет в единичное состояние независимо от состояния входов J и К на момент спада. Аналогично, если триггер находится в единичном состоянии и во время действия тактового импульса на всех входах К была кратковременно лог. 1, по спаду тактового импульса триггер перейдет в нулевое состояние независимо от состояния входов J и К.

Предельная частота работы триггера К155ТВ1 10 МГц.

МикросхемаТВ6 (рис. 16) - сдвоенный JK-триггер. Каждый триггер имеет вход для подачи тактовых импульсов С, входы для подачи информации J и К, вход сброса R. Приоритетом пользуется вход R -при подаче на него лог. 0 триггер устанавливается в нулевое состояние, при котором на прямом выходе триггера - лог. 0, на инверсном -лог. 1. При лог. 1 на входе R возможна запись информации со входов J и К. Переключение триггера происходит по спаду импульсов положительной полярности на входе С. Если перед спадом сигнала на входе С на входе J лог. 1, на входе К лог. 0, триггер установится в единичное состояние, если на входе J лог. 0, на входе К лог. 1 - в нулевое. Если на входах J и К лог. 0, переключение по спаду импульса на входе С не произойдет; если на обоих входах лог. 1, триггер по спаду на входе С переключится в противоположное состояние. Для переключения триггера важна информация на входах J и К непосредственно перед переходом на входе С уровня лог. 1 в лог. 0, поэтому информация на входах J и К может меняться как при лог. 0, так и при лог. 1 на входе С. Предельная частота работы триггеров микросхем К555ТВ6 и КР1533ТВ6 - 30 МГц.

МикросхемаТВ9 (рис. 16) - также два JK-триггера, имеющих дополнительно ко входам триггеров К555ТВ6 еще входы установки в единичное состояние S при подаче лог. 0 на вход S. В остальном логика работы этих триггеров аналогична логике работы триггера ТВ6.

Предельная частота работы триггеров микросхем К555ТВ9 и КР1533ТВ9 - 30 МГц.

Микросхема ТВ10 (рис. 16) - два JK-триггера, функционирующих аналогично триггерам микросхем ТВ9, но отличающихся наличием лишь одного установочного входа. Этот вход можно считать входом установки в состояние 1 (вход S), можно считать входом сброса (вход R), в этом случае входы J и К и прямой и инверсный выходы меняются местами. Оба варианта графического обозначения триггера приведены на рис. 16.

МикросхемаТВ11 (рис. 16) - два аналогичных JK-триггера со входами установки и сброса, входы сброса и тактовые входы этих триггеров соответственно объединены.

Предельная частота работоспособности триггеров КР1533ТВ10 и КР1533ТВ11- 30 МГц, триггеров КР531ТВ9- КР531ТВ11 -80 МГц. Входные токи триггеров серии КР531 по некоторым входам увеличены - для выводов S всех триггеров - 7 мА, R для КР531ТВ11 - 14 мА, С для КР531ТВ9 и КР531ТВ10- 4 мА, для КР531ТВ11-8 мА.

Микросхема ТВ15 - сдвоенный JK-триггер (рис. 16), каждый из которых имеет входы: R и S - для установки в 0 и 1 при подаче лог. 0 на соответствующий вход, С - для подачи тактовых импульсов и J и К-информационные. Особенность микросхемы в том, что входы К - инверсные. В отличие от описанных выше JK-триггеров переключение происходит по спаду импульсов отрицательной полярности на входе С.

Счетный режим переключения триггера на каждый импульс осуществляется при подаче на вxoд J лог. 1, на вход К - лог. 0. Если на входы J и К подать лог. 1, по спаду импульса отрицательной полярности произойдет установка триггера в 1, если на эти входы подать лог. 0 - в 0. Объединение входов J и К превращает триггеры микросхемы в D-триггеры, аналогичные триггерам микросхем ТМ2, описываемых ниже. При J = 0, К = 1 происходит блокировка переключения, и триггеры микросхемы ТВ15 на импульсы на входе С не реагируют. Сигналы на входах J и К можно изменять как при лог. 0, так и при лог. 1 на входе С - для переключения триггера играют роль сигналы на этих входах лишь непосредственно перед переходом напряжения на входе С с лог. 0 на лог. 1.

Предельная частота функционирования триггеров К155ТВ15 -25 МГц, КР1533ТВ15 - 34 МГц.

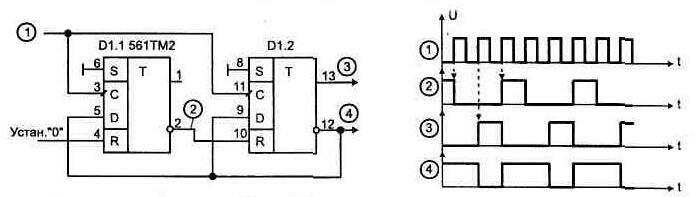

МикросхемаТМ2 (рис. 16) содержит два D-триггера. Триггер D-типа имеет вместо входов J и К один вход D. По входам R и S

D-триггер работает так же, как и JK-триггер. Если на входе D лог. 0, по спаду импульса отрицательной полярности на входе С триггер устанавливается в нулевое состояние, при лог. 1 на входе D по спаду импульса отрицательной полярности на входе С триггер устанавливается в единичное состояние.

Для получения режима счетного триггера вход D соединяют с инверсным выходом триггера, в этом случае триггер меняет свое состояние на противоположное по спадам входных импульсов отрицательной полярности.

Предельная частота функционирования триггеров К155ТМ2 -15 МГц, К555ТМ2 - 25 МГц, КР1533ТМ2 - 40 МГц, КР531ТМ2 -80 МГц. Входные токи микросхемы КР531ТМ2 в состоянии лог. 0 составляют 4 мА по входам С и S, 6 мА по входу R, 2 мА по входу D.

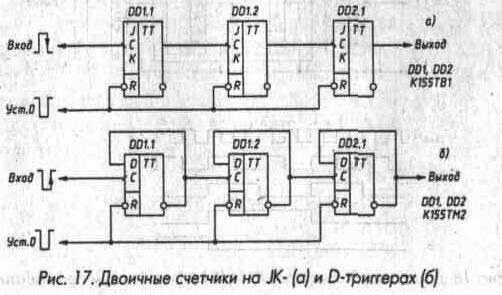

На основе JK- и D-триггеров ТМ2 строятся счетчики и делители частоты.

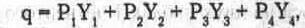

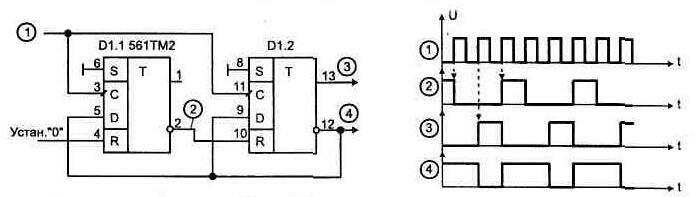

Для построения двоичных счетчиков счетные входы JK-триггеров К155ТВ1, ТВ6, ТВ9 - ТВ 11 соединяют с прямыми выходами предыдущих триггеров, а D-триггеров ТМ2 и JK-триггеров ТВ 15 с инверсными (рис. 17). Отличие в подключении входов связано с тем, что триггеры микросхем ТМ2 и ТВ 15 срабатывают по спаду импульсов отрицательной полярности, а остальные - по спаду импульсов положительной полярности.

Состояние счетчика (число поступивших на его вход импульсов после установки в 0) однозначно определяется состоянием его триггеров. В частности, для четырехразрядных счетчиков состояние может быть определено по формуле

где Yi= 0 или 1 - состояние 1-го триггера (i = 1 - 4, начиная со входа счетчика); Рj= 2^i - 1 - вес i-го разряда счетчика. О таких счетчиках

говорят, что они работают в весовом коде 1-2-4-8. Счетчик может быть построен так, что его весовой код будет отличаться от рассмотренного. Так, для четырехразрядных счетчиков получили распространение коды 1-2-4-6, 1-2-2-4 и др. Существуют такие структуры счетчиков, состояние которых не может быть выражено приведенной выше формулой. О таких счетчиках говорят, что они работают в невесовом коде. Их состояния определяют по временным диаграммам или таблицам переходов. Сказанное о четырехразрядных счетчиках распространяется на счетчики любой разрядности.

Делители частоты (далее просто делители) отличаются от счетчиков тем, что вних используется только один выход - выход последнего триггера. Таким образом, n-разрядный двоичный счетчик всегда можно рассматривать как делитель на 2^n.

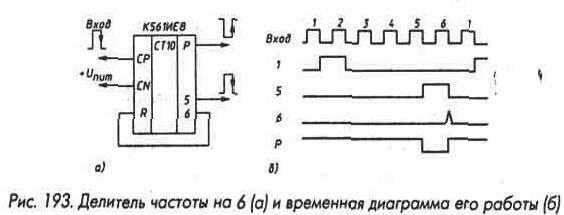

Часто необходимо осуществить деление частоты на некоторое целое число т, не являющееся степенью двойки, в таких случаях обычно используют n-разрядный двоичный счетчик (2^n >m) и вводом дополнительных логических связей обеспечивают пропуск 2^n - m состояний в процессе счета. Этого можно достигнуть, например, принудительной установкой счетчика в 0 при достижении состояния m или принудительной установкой счетчика в состояние 2^n - m при его переполнении.

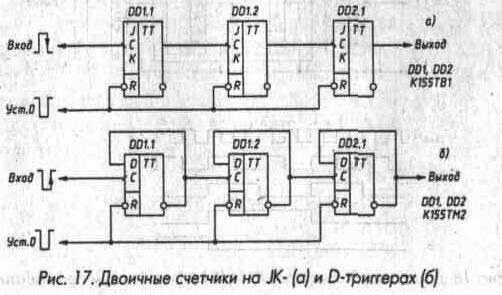

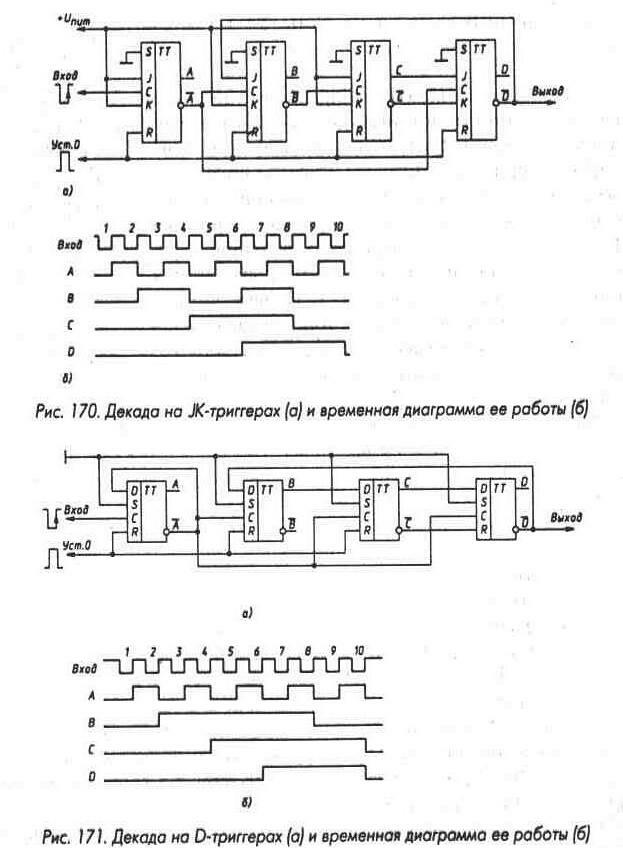

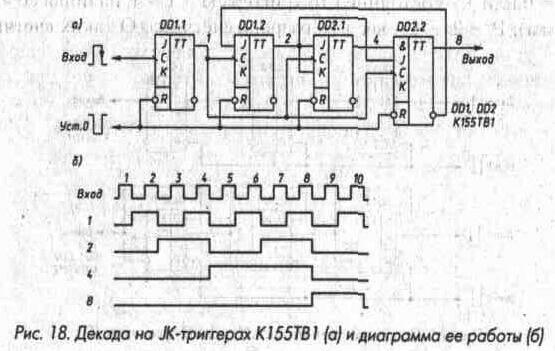

Возможны и другие способы. Например, наиболее часто применяемая декада (счетчик с коэффициентом пересчета 10) нa JK-триггерах К155ТВ1 строится по схеме рис. 18 (а). При подаче импульсов с 1-го по 8-й декада работает как обычный двоичный счетчик импульсов. К моменту подачи восьмого импульса на двух входах J четвертого

триггера формируется уровень лог. 1, восьмым импульсом этот триггер переключается в единичное состояние и уровень лог. 0 с его инверсного выхода, подаваемый на вход J второго триггера, запрещает его переключение в единичное состояние под действием десятого импульса. Десятый импульс восстанавливает нулевое состояние четвертого триггера, и цикл работы делителя повторяется.

Декада на рис. 18 (а) работает в весовом коде 1-2-4-8. Временная диаграмма ее работы приведена на рис. 18 (б).

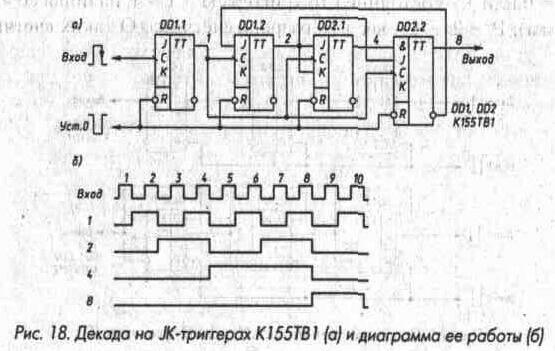

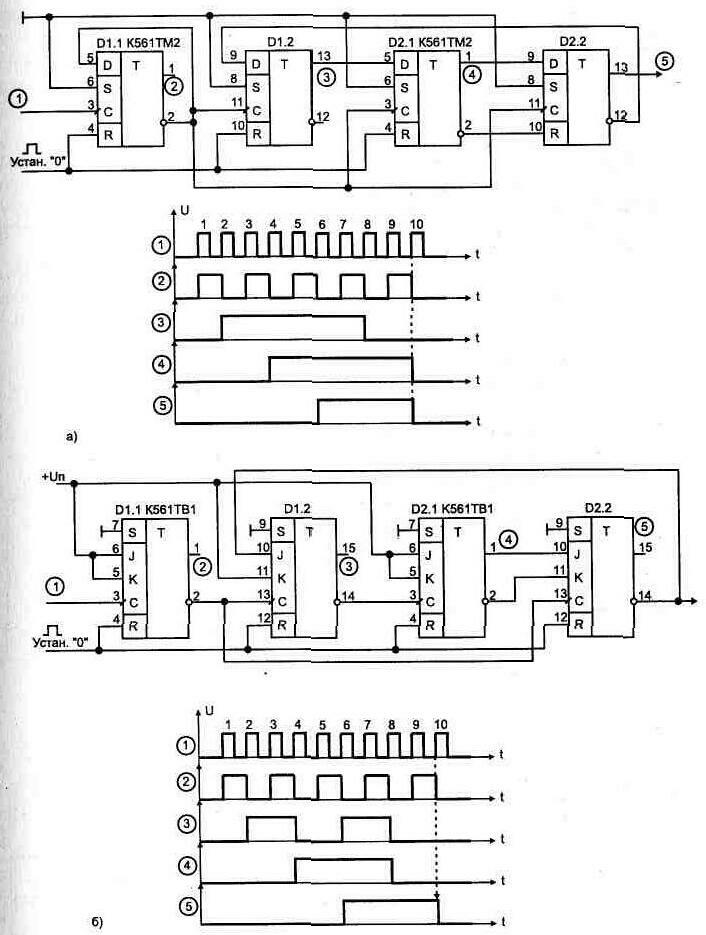

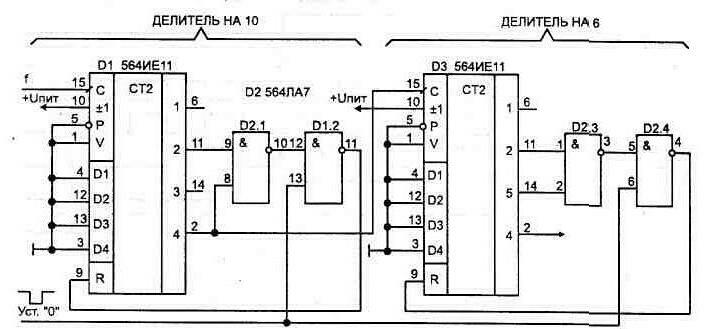

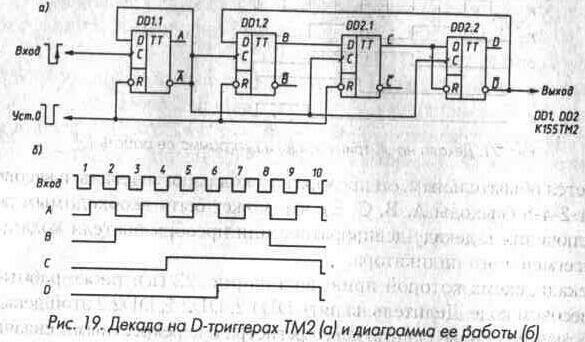

Декада на D-триггерах, схема которой приведена на рис. 19 (а), работает в невесовом коде. Временная диаграмма ее работы приведена на рис. 19 (б).

Построение счетчиков с коэффициентом пересчета 10 (декад) на триггерах ТВ6, ТВ9, ТВ10 отличается от построения на триггерах К155ТВ1, так как у триггеров указанных микросхем по одному входу J и К.

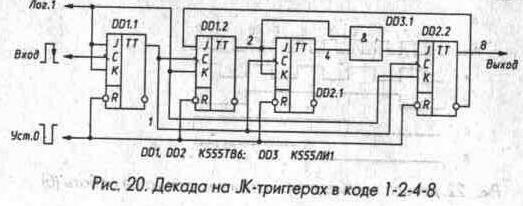

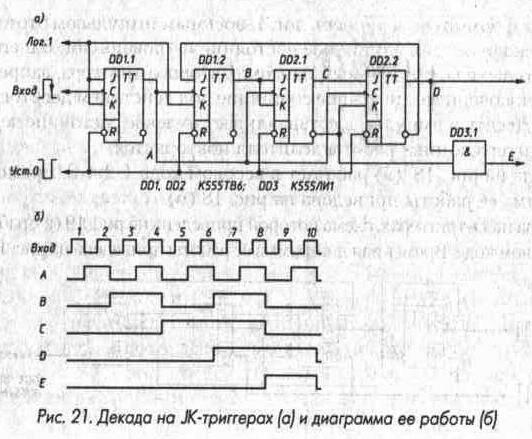

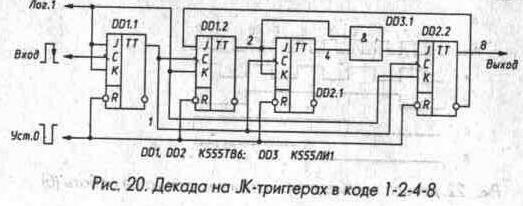

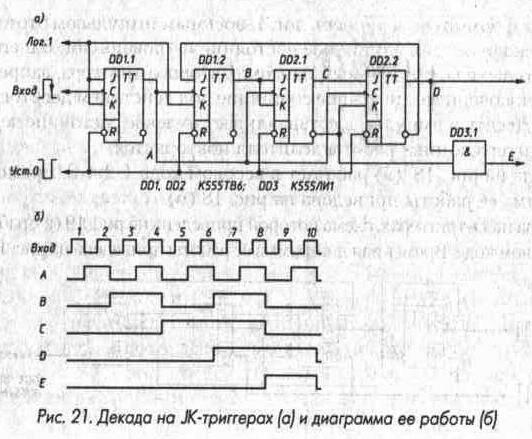

На рис. 20 приведена схема декады, работающей в весовом коде 1-2-4-8. Для увеличения числа входов J до необходимого использован один элемент микросхемы К555ЛИ1. На рис. 21 (а) приведена схема декады, выходной код которой не является весовым. Работа декады проиллюстрирована на диаграмме рис. 21 (б). Элемент DD3 не

является обязательным, он преобразует код работы декады в весовой код 1-2-4-8 (выходы А, В, С, Е), что может быть необходимым для подключения к декаде дешифратора или преобразователя кода для семисегментного индикатора.

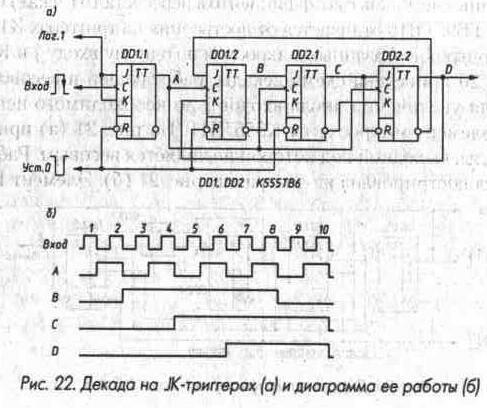

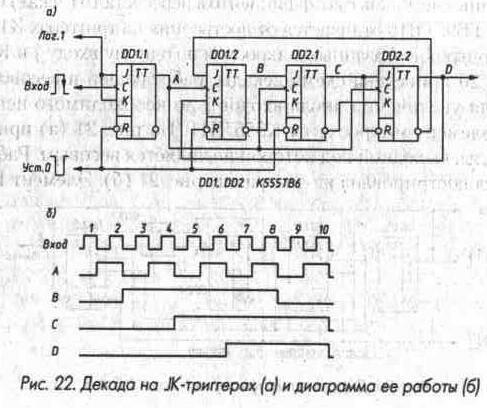

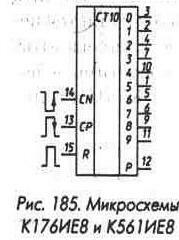

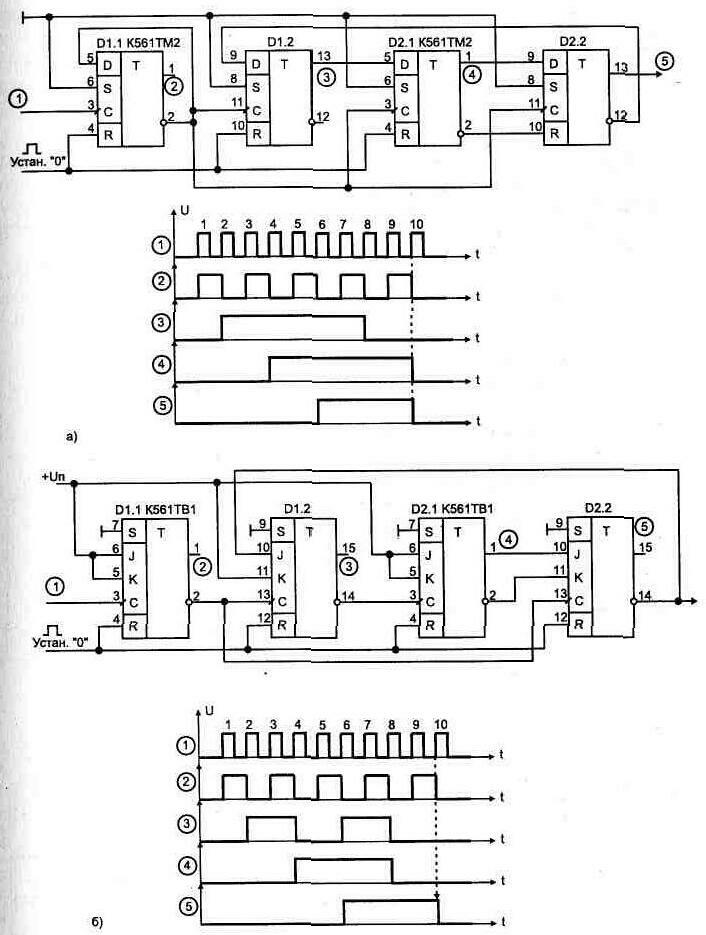

Декада, схема которой приведена на рис. 22 (а), также работает в невесовом коде. Делитель на пять DD1.2, DD2.1, DD2.2 этой декады выполнен на основе сдвигающего регистра с перекрестными связями

так же, как и декады на D-триггерах рис. 19 (а). Коэффициент деления шесть такого регистра уменьшен до пяти за счет подключения входа R триггера DD2.2 к прямому выходу триггера DD2.1. Временная диаграмма работы приведена на рис. 22 (б).

МикросхемаТР2 (см. рис. 16) - четыре RS-триггера. Два триггера микросхемы

имеют по одному входу R и S, два других - по одному входу R и по два входа S. Сброс и установка триггеров в 1 происходят при подаче лог. 0 соответственно на входы R и S. Входы S тех триггеров, гдеих два, собраны как логический элемент ИЛИ для сигналов лог. 0, поэтому для установки триггеров в состояние 1 достаточно подать лог. 0 на один из входов S, состояние второго при этом не играет роли. Если на входы R и S триггера подать лог. 0, на выходе триггера - лог. 1. Состояние триггера после снятия сигналов лог. 0 со входов R и S будет определяться тем, с какого из входов лог. 0 будет снят последним.

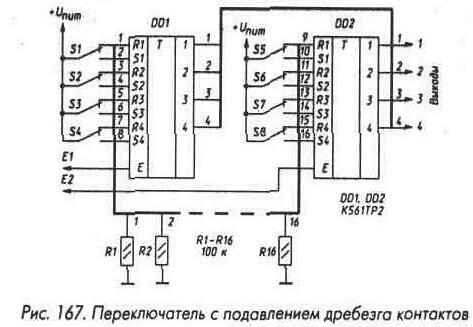

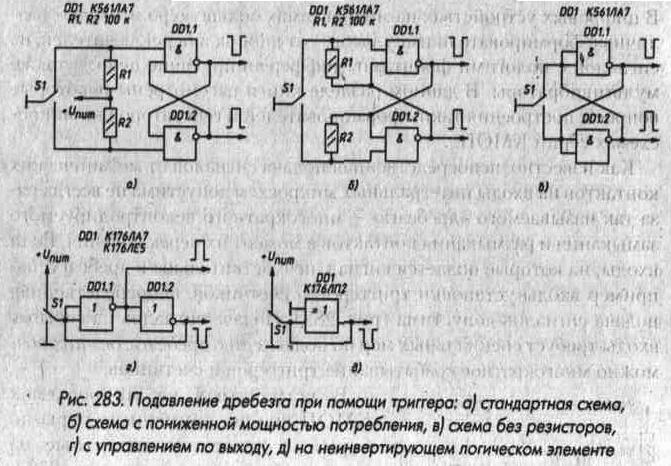

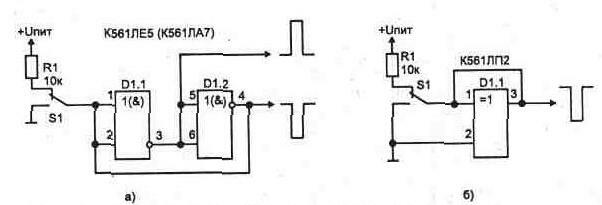

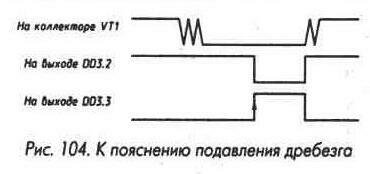

Микросхему ТР2 можно использовать для подавления дребезга контактов (рис. 23) и в других случаях.

Рис. 16 Микросхемы триггеров

Рис. 17 Двоичные счетчики на JK и D-триггерах

Рис. 18 Декада на JK-триггерах К155ТВ1 и диаграмма ее работы

Рис. 19 Декада на D-триггерах К155ТМ1 и диаграмма ее работы

Рис. 20 Декада на JK-триггерах в коде 1-2-4-8

Рис. 21 Декада на JK-триггерах и диаграмма ее работы

Рис. 22 Декада на JK-триггерах и диаграмма ее работы

Рис. 23 Подавитель дребезга на микросхеме К155ТР2

Ф.1 Определение состояния четырехразрядных счетчиков

1.3.2 Счетчики.

1.3.2. Счетчики

В состав рассматриваемых серий ТТЛ-микросхем входит большое число счетчиков и делителей частоты, различающихся по своим свойствам и назначению.

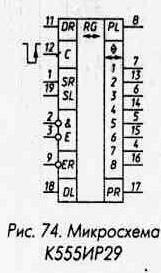

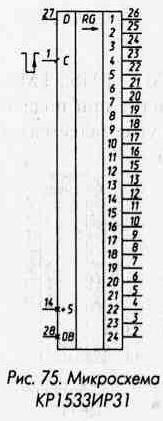

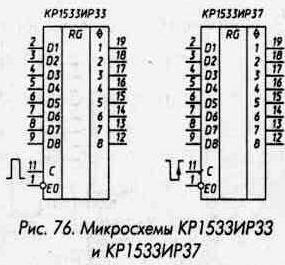

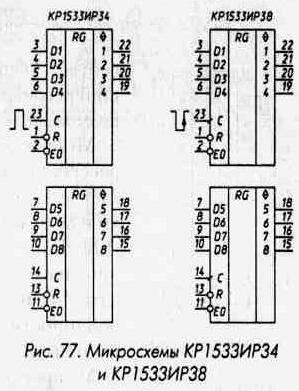

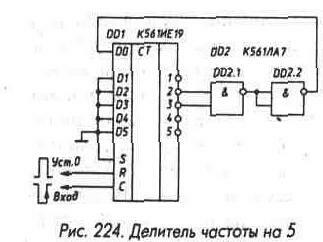

МикросхемаК155ИЕ1 (рис. 24) - делитель частоты на 10. Установка триггеров микросхемы в 0 осуществляется подачей лог. 1 одновременно на два объединенных по схеме И входа R. Рабочая полярность входных счетных импульсов, подаваемых на входы С, отрицательная. Импульсы можно подавать или отдельно на каждый из входов (на второй вход

должна при этом подаваться лог. 1), или одновременно на оба входа. Одновременно с каждым десятым входным импульсом на выходе формируется равный ему по длительности выходной импульс отрицательной полярности. Многокаскадные делители частоты можно строить, соединяя входы С последующих каскадов с выходами предыдущих.

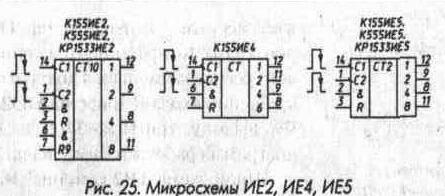

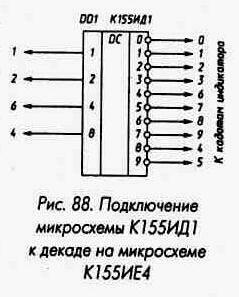

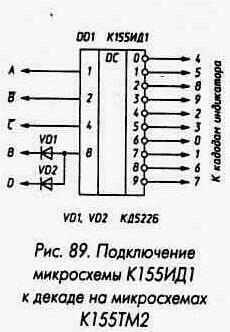

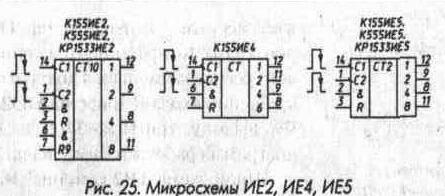

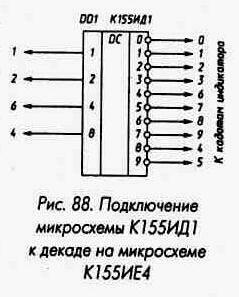

МикросхемыИЕ2, К155ИЕ4 и ИЕ5 (рис. 25) содержат по четыре счетных триггера. В каждой микросхеме один из триггеров имеет отдельный вход С1 и прямой выход, три оставшихся триггера соединены между собой так, что образуют делитель на 8 в микросхеме ИЕ5,

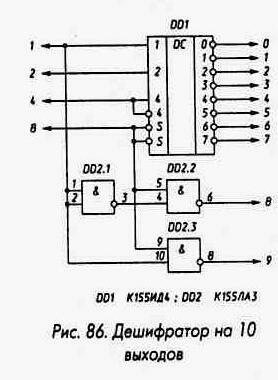

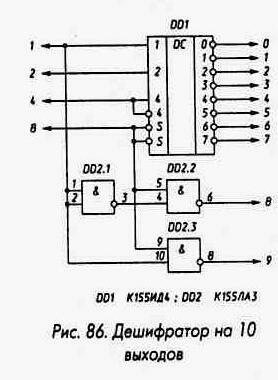

на 6 в К155ИЕ4 и на 5 в ИЕ2. При соединении выхода первого триггера с входом С2 цепочки из трех триггеров образуются соответственно делители на 16, 12 и 10. Делители на 10 и 16 работают в коде 1-2-4-8, делитель на 12 - в коде 1-2-4-6. Микросхемы имеют по два входа R установки в 0, объединенные по схеме И. Сброс (установка в 0) триггеров производится при подаче лог. 1 на оба входа R. Микросхема ИЕ2 имеет, кроме того, входы R9 для установки в состояние 9, при котором первый и последний триггеры декады находятся в единичном состоянии, остальные - в нулевом.

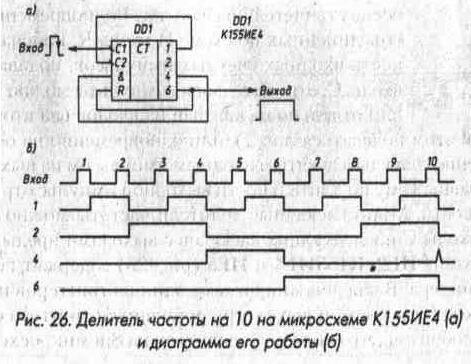

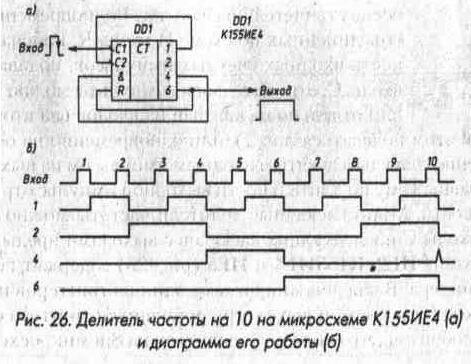

Наличие входов установки, объединенных по схеме И, позволяет строить делители частоты с различными коэффициентами деления в пределах 2-6 без использования дополнительных логических элементов. На рис. 26 приведены схема декады на микросхеме К155ИЕ4 и ее временная диаграмма. До прихода десятого импульса декада работает как делитель частоты на 12. Десятый импульс переводит триггеры микросхемы в состояние 10, при котором на выходах 4 и 6 микросхемы формируются уровни лог. 1. Эти уровни, поступая на входы

R микросхемы, переводят ее в 0, в результате чего коэффициент пересчета К становится равным 10

Для установки рассмотренной декады в 0 внешним сигналом необходимо введение в нее логических элементов И-НЕ (рис 27)

В табл. 4 приведены номера выводов микросхем, которые нужно соединить между собой для получения различных К Все делители, полученные соединением выводов по табл. 4, работают по одно

му принципу - при достижении состояния, соответствующего необходимому коэффициенту пересчета, происходит установка счетчика в 0. Исключение составляет делитель на 7 на микросхеме ИЕ2. В этом делителе после подсчета шести импульсов на входах R9 формируются уровни лог. 1, поэтому из состояния 5 делитель сразу переходит в состояние 9, минуя 6,7 и 8 Код работы этого делителя - невесовой

Делители на микросхемах ИЕ5 и ИЕ2 работают в весовом коде 1-2-4-8, на микросхеме К155ИЕ4 - в коде 1-2-4-6 при использовании входа 14 и в коде 1-2-3 - при использовании входа 1.

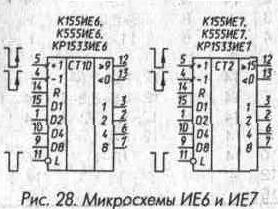

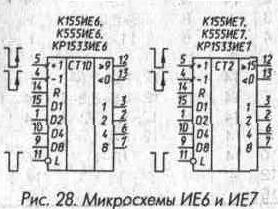

МикросхемыИЕ6 и ИЕ7 - реверсивные счетчики. Первый из них - двоично-десятичный, второй - двоичный Оба работают в коде 1-2-4-8 Цоколевка обеих микросхем одинакова (рис 28), различие в том, что первый считает до 10, второй до 16

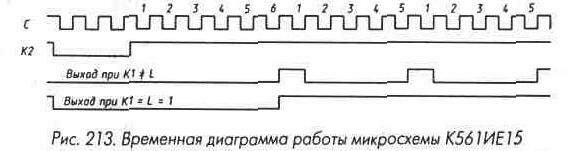

Рассмотрим для примера работу микросхемы ИЕ6 В отличие от рассмотренных ранее счетчиков, эта микросхема имеет большее число

Таблица 4

|

К |

К155ИЕ2 |

К155ИЕ4 |

К155ИЕ5 |

||||||

|

Вход |

Вых. |

Соединить выводы |

Вход |

Вых. |

Соединить выводы |

Вход |

Вых. |

Соединить выводы |

|

|

2 |

14 |

12 |

14 |

12 |

- |

14 |

12 |

- |

|

|

3 |

1 |

8 |

9-2,8-3 |

1 |

9 |

- |

1 |

8 |

9-2,8-3 |

|

4 |

1 |

8 |

11-2-3 |

1 |

8 |

11-6,8-7 |

1 |

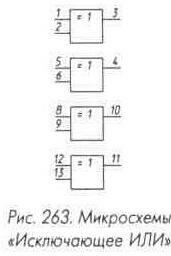

8 |

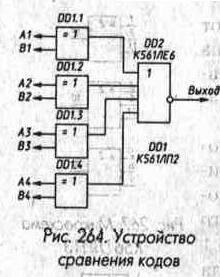

- |

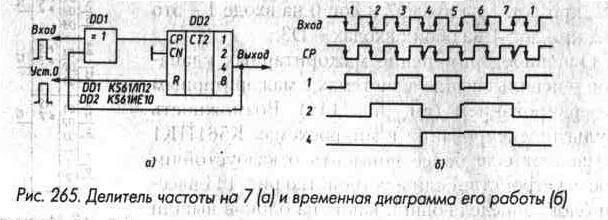

|

5 |

1 |

11 |

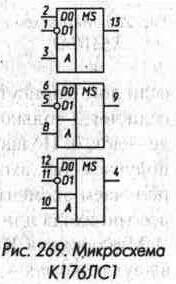

- |

1 |

8 |

9-6,8-7 |

1 |

11 |

9-2,11-3 |

|

6 |

14 |

8 |

12-1,9-2,8-3 |

1 |

8 |

- |

1 |

11 |

8-2,11-3 |

|

7 |

14 |

11 |

12-1,9-6,8-7 |

14 |

8 |

12-1-6,8-7 |

- |

- |

- |

|

8 |

14 |

8 |

12-1,11-2-3 |

14 |

8 |

12-1,11-6,8-7 |

1 |

11 |

- |

|

9 |

14 |

11 |

12-1-2,11-3 |

- |

- |

- |

14 |

11 |

12-1-2,11-3 |

|

10 |

14 |

11 |

12-1 |

14 |

8 |

12-1,9-6,8-7 |

14 |

11 |

12-1,9-2,11-3 |

|

12 |

- |

14 |

8 |

12-1 |

14 |

11 |

12-1,8-2,11-3 |

||

|

16 |

- |

- |

- |

- |

- |

- |

14 |

11 |

12-1 |

выходов и входов Входы +1 и -1 служат для подачи тактовых импульсов, +1 - при прямом счете, -1 - при обратном. Вход R служит для установки счетчика в 0, вход L - для предварительной записи в счетчик информации, поступающей по входам D1 - D8.

Установка триггеров счетчика в 0 происходит при подаче лог 1 на вход R, при этом на входе L должна быть лог. 1. Для предварительной записи в счетчик любого числа от 0 до 9 его код следует подать на входы D1 - D8 (D1 - младший разряд, D8 - старший), при этом на входе R должен быть лог 0, и на вход L подать импульс отрицательной полярности

Режим предварительной записи можно использовать для построения делителей частоты с перестраиваемым коэффициентом деления для учета фиксированной частоты (например, 465 кГц) в цифровой шкале радиоприемника Если этот режим не используется, на выходе L должен постоянно поддерживаться уровень лог 1

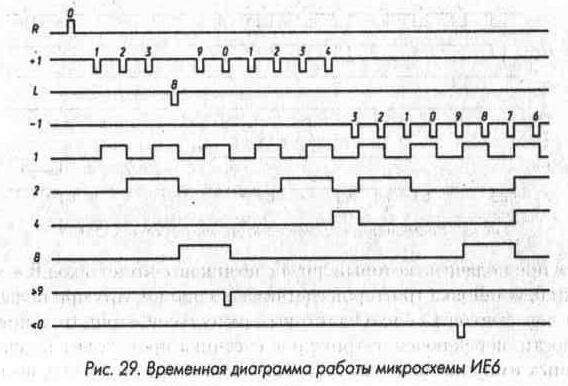

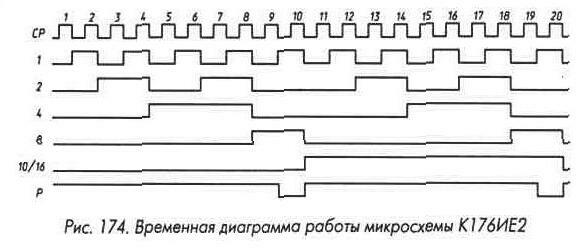

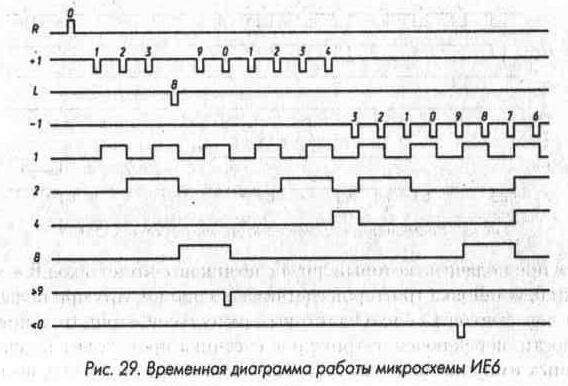

Прямой счет осуществляется при подаче импульсов отрицательной полярности на вход +1, при этом на входах -1 и L должна быть лог 1, на входе R - лог 0 Переключение триггеров счетчика происходит по спадам входных импульсов, одновременно с каждым десятым входным импульсом на выходе >=9 формируется отрицательный выходной импульс переполнения, который может подаваться на вход +1 следующей микросхемы многоразрядного счетчика Уровни на выходах 1-2-4-8 счетчика соответствуют состоянию счетчика в данный момент (в двоичном коде) При обратном счете входные импульсы подаются на вход -1, выходные импульсы снимаются с выхода <=0 Пример временной диаграммы работы счетчика приведен на рис. 29.

Первый импульс установки в 0 устанавливает все триггеры счетчика в 0. Три следующих импульса, поступающих на вход +1, переводят счетчик в состояние 3, которому соответствуют лог. 1 на выходах 1 и 2 и лог 0 - на 4 и 8. Если на входах D1 - D4 лог. 0, на входе D8 лог. 1, импульс на входе L устанавливает счетчик в состояние 8 Следующие

шесть импульсов, поступающие на вход +1, переводят счетчик последовательно в состояния 9,0,1,2,3,4 Одновременно с импульсом, переводящим счетчик в 0, на выходе S9 появляется выходной импульс прямого счета Следующие импульсы, поступающие на вход -1, изменяют состояние счетчика в обратном порядке 3, 2, 1,0,9,8 и т д

Одновременно с импульсом обратного счета, переводящим счетчик в состояние 9, на выходе <=0 появляется выходной импульс.

В микросхеме ИЕ7 импульс на выходе =>15 появляется одновременно с импульсом на входе +1 при переходе счетчика из состояния 15 в состояние 0, а на выходе <=0 - при переходе счетчика из 0 в 15 одновременно с импульсом на входе -1.

Предельная частота функционирования микросхем К155ИЕ6, К155ИЕ7 - 15 МГц, К555ИЕ6 и К555ИЕ7 - 25 МГц, КР1533ИЕ6 и КР1533ИЕ7 - 30 МГц.

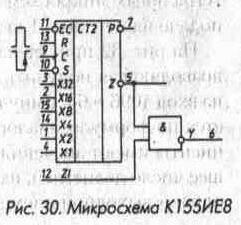

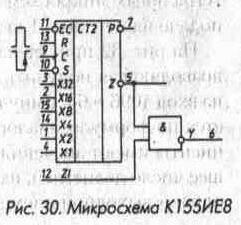

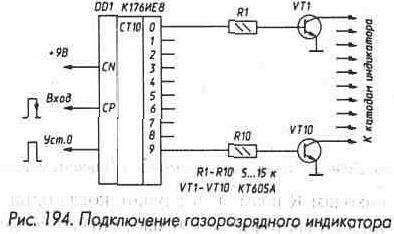

МикросхемуК155ИЕ8 обычно называют делителем частоты с переменным коэффициентом деления, однако это не совсем точно. Эта микросхема содержит шестиразрядный двоичный счетчик, элементы совпадения, позволяющие выделять не совпадающие между собой импульсы - каждый второй, каждый четвертый, каждый восьмой и т. д. и управляемый элемент И-ИЛИ, который позволяет подавать на выход часть или все выделенные импульсы, в результате чего сред-

няя частота выходных импульсов может изменяться от 1/64 до 63/64 частоты входных импульсов. Графическое обозначение микросхемы приведено на рис. 30, пример временной диаграммы ее работы - на рис. 31. Для наглядности на рис. 30 вынесен логический элемент И-НЕ, входящий в микросхему. Микросхема имеет следующие входы: инверсный вход ЕС - разрешения

счета, при подаче на который лог. 1 счетчик не считает, вход R - установки 0, установка триггеров счетчика в 0 происходит при подаче на него лог. 1; вход С - вход тактовых импульсов отрицательной полярности, переключение триггеров счетчика происходит по спадам входных импульсов; входы XI - Х32 позволяют управлять выдачей отрицательных выходных импульсов, совпадающих по времени с входными, на выход Z. На рис. 31 в качестве примера показано, какие импульсы выделяются на выходе Z при подаче лог. 1 на входы:

Х32 (диаграмма Х32), Х16 (диаграмма Х16) и Х8 (диаграмма Х8). В этих случаях на выходе Z выделяется соответственно 32, 16 или 8 равномерно расположенных импульсов. Если же одновременно подать лог. 1 на несколько входов, например, на Х32 и Х8, то, как показано на диаграмме Z, на выходе Z выделится 40 импульсов, но расположенных неравномерно. В общем случае число импульсов N на выходе Z за период счета составит

N = 32 х Х32 + 16 х Х16 + 8 х Х8 + 4 х Х4 + 2 х Х2 + X1, где X1-Х32 принимают значения соответственно 1 или 0 в зависимости от того, подана или нет лог. 1 на соответствующий вход.

На выходе Р выделяется отрицательный импульс, фронт которого совпадает со спадом 63-го тактового импульса, спад - со спадом 64-го. Этот импульс может использоваться при каскадном соединении интегральных микросхем К155ИЕ8. Вход S - вход стробирования, при подаче на него лог. 1 выдача импульсов на выходе Z прекращается.

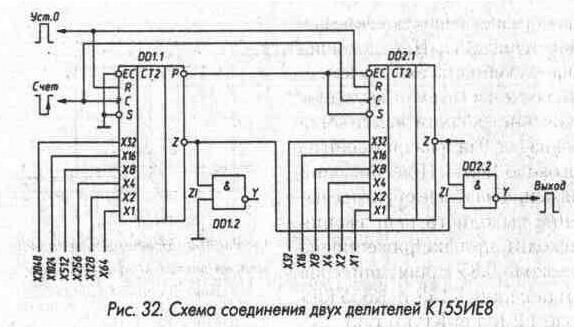

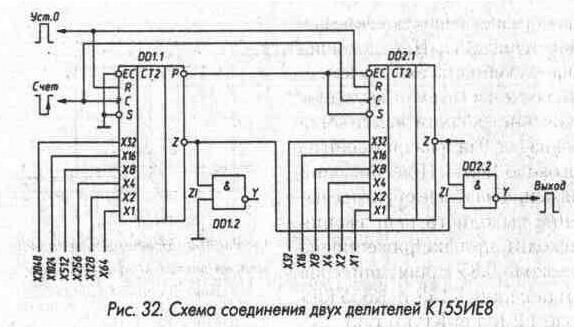

На рис. 32 приведена схема соединения двух делителей К155ИЕ8, позволяющая получить на выходе от 1 до 4095 импульсов при подаче на вход 4096 =64^2 импульсов. Число импульсов на выходе подсчитывается по формуле, аналогичной приведенной выше, в которой коэффициенты имеют значения от 2048 до 1. Если требуется соединить большее число делителей, их соединение производится аналогично рис. 32, однако выходной элемент И-НЕ, выполняющий функцию ИЛИ-НЕ

для отрицательных импульсов, поступающих с выходов Z делителей, необходимо использовать из отдельной микросхемы И-НЕ или И.

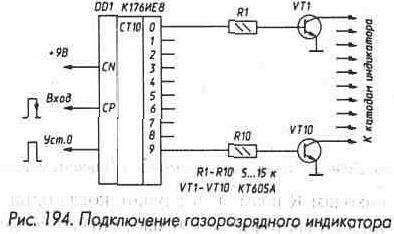

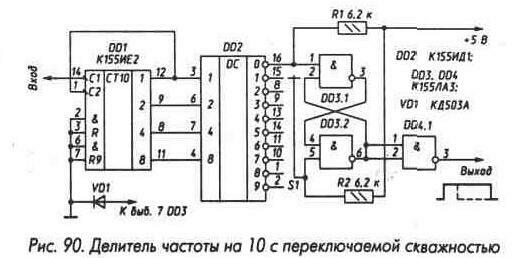

МикросхемаИЕ9 (рис. 33) - синхронный десятичный счетчик с возможностью параллельной записи информации по фронту тактового импульса, имеет девять входов. Подача лог. 0 на вход R независимо от состояния других входов приводит к установке триггеров микросхемы в состояние 0. Для обеспечения режима счета на входе R необходимо подать лог. 1, тот же сигнал должен быть подан на входы разрешения параллельной записи EL, разрешения ЕС, разрешения выдачи сигнала переноса ER Изменение состояния триггеров счетчика при счете происходит по спаду импульсов отрицательной полярности, подаваемых на вход С.

При подаче лог. 0 на вход EL микросхема переходит в режим параллельной записи информации со входов D1 - D8. Запись происходит по спадам импульсов отрицательной полярности на входе С, что позволяет использовать микросхему в режиме сдвигающего регистра. При записи на входе R должна быть лог. 1, сигналы на входах ЕС и ЕР произвольны.

На выходе переноса Р лог. 1 появляется в том случае, когда счетчик находится в состоянии 9, а на входе ЕР - лог. 1, в остальных случаях на выходе Р лог. 0. Подача лог. 0 на вход ЕР запрещает выдачу лог. 1 на выходе Р и счет импульсов. Подача лог. 0 на вход ЕС запрещает счет, но не запрещает выдачу сигнала переноса. Сигнал запрета счета (лог. 0 на входах ЕС и ЕР) действует лишь в том случае, если он полностью перекрывает по длительности импульс отрицательной полярности на входе С, в том числе он может совпадать с ним по времени.

Для обеспечения параллельной записи лог. 0 на вход EL информация на входы D1 - D8 может быть подана как при лог. 1, так и при лог. 0 на входе С и удерживаться до момента перехода лог. 0 на входе С в лог. 1, когда и произойдет запись.

Для обеспечения счета с числа, введенного в микросхему при параллельной записи, лог 0 на входе EL должен быть изменен на лог. 1 или одновременно с переходом лог. 0 в лог. 1 на входе С, или при лог. 1 на входе С.

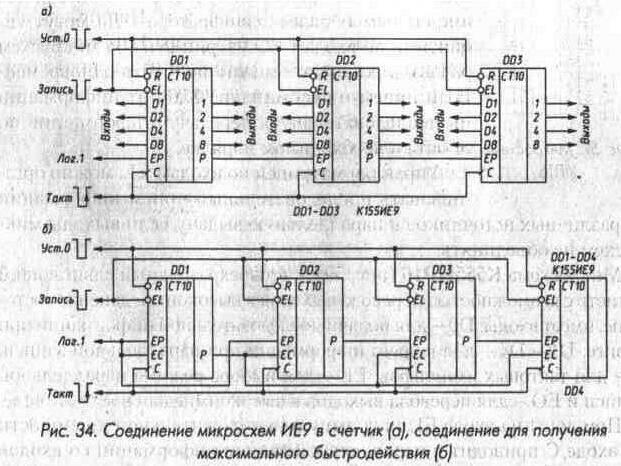

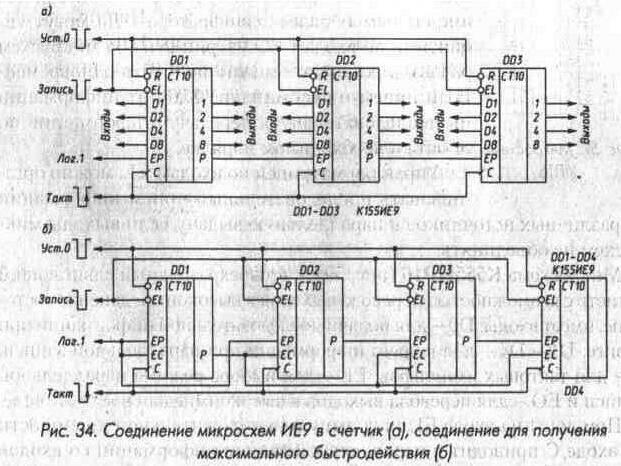

На рис. 34 (а) приведена схема соединения микросхем ИЕ9 в многоразрядный синхронный счетчик, которая снижает быстродействие счетчика, так как для его нормальной работы необходимо, чтобы сигнал переноса от младшего разряда прошел через все микросхемы до старшего разряда до подачи очередного тактового импульса. Для получения максимального быстродействия многоразрядного счетчика, равного быстродействию отдельной микросхемы, микросхемы можно соединить по схеме рис. 34 (б). В этом случае сигнал переноса с выхода Р микросхемы DD1 разрешает работу остальных микросхем, соединенных в счетчик по схеме рис. 34 (а), лишь в те моменты, когда микросхема DD1 находится в состоянии 9, поэтому от счетчика DD2 - DD9 требуется быстродействие в 10 раз меньшее быстродействия микросхемы DD1, что обеспечивается при любой практически встречающейся длине счетчика.

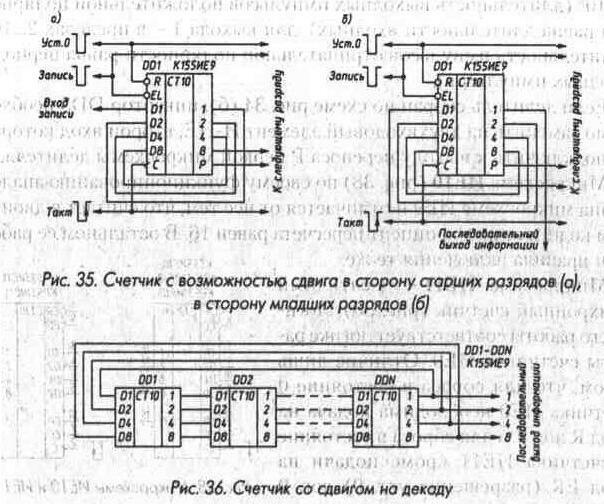

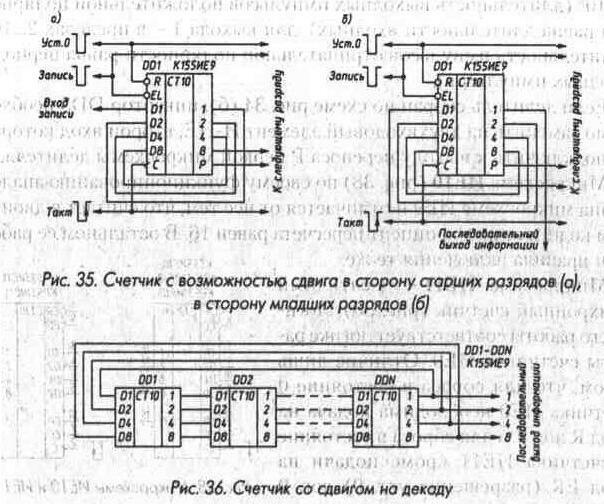

Как уже указывалось выше, микросхемы ИЕ9 могут работать в режиме сдвигающего регистра. Для обеспечения такого режима необходимо входы D1 - D8 соединить с выходами 1-2-4-8 в нужном порядке. Для сдвига информации на один двоичный разряд по каждому тактовому импульсу в сторону старших разрядов соединение необходимо произвести в соответствии с рис. 35 (а). Для обеспечения динамической индикации удобно сдвигать информацию сразу на один десятичный разряд, а сдвигающий регистр замыкать в кольцо. Такая возможность проиллюстрирована на рис. 36.

На рис. 36 не показаны цепи подачи импульсов и управляющих сигналов, которые могут быть выполнены в соответствии с рис. 34 (а) или 34 (б). Роль входа разрешения сдвига выполняет вход Запись. Естественно, что при соединении микросхем в соответствии с рис. 35,36 параллельная запись информации в микросхемы невозможна.

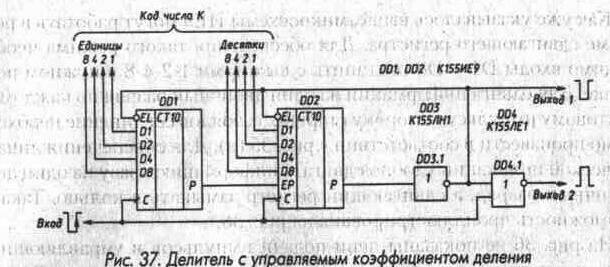

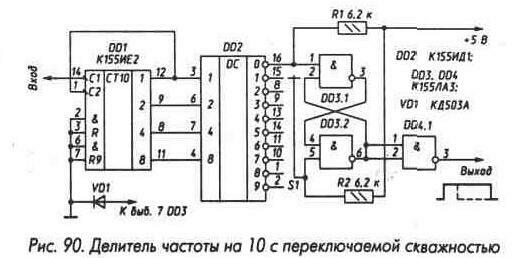

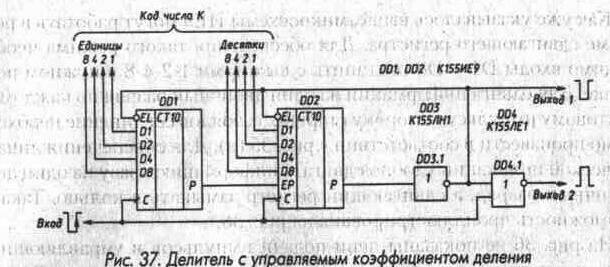

Микросхемы ИЕ9 удобно использовать в делителе с переключаемым коэффициентом пересчета. Для получения указанного режима достаточно сигнал переноса старшего разряда одноразрядного или многоразрядного счетчика через инвертор подать на вход разрешения записи, а на входы D1 - D8 подать код, определяющий коэффициент пересчета (рис. 37).

При установке счетчика в процессе счета в состояние 99...9 счетчик перейдет в режим параллельной записи и при подаче следующего тактового импульса вместо перехода в состояние 00...0 произойдет запись параллельного кода, поданного на входы D1 - D8 микросхем. В результате общий коэффициент пересчета N уменьшится на величину К, соответствующую численному значению этого кода, и составит

Коэффициент пересчета может меняться для выхода 2 в пределах 1...10^м (длительность выходных импульсов положительной полярности равна длительности входных), для выхода 1 - в пределах 2...10^м (длительность импульсов отрицательной полярности равна периоду входных импульсов).

Если делитель собран по схеме рис. 34 (б), инвертор DD3 необходимо заменить на двухвходовый элемент И-НЕ, второй вход которого подключить к выходу переноса Р первой микросхемы делителя.

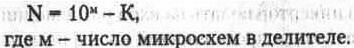

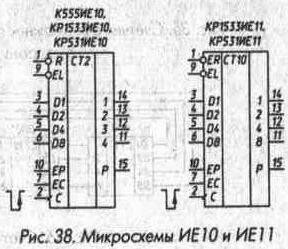

МикросхемаИЕ10 (рис. 38) по своему функционированию аналогична микросхеме ИЕ9 и отличается от нее тем, что считает в двоичном коде, и ее коэффициент пересчета равен 16. В остальном ее рабо

та и правила включения те же.

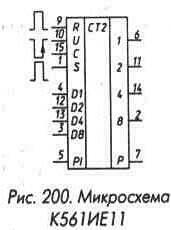

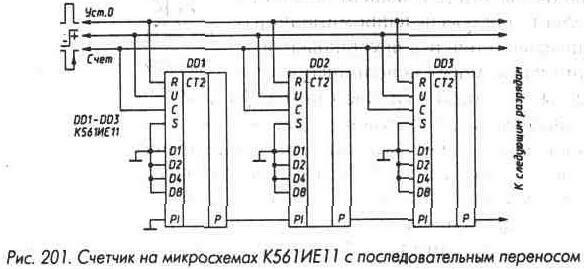

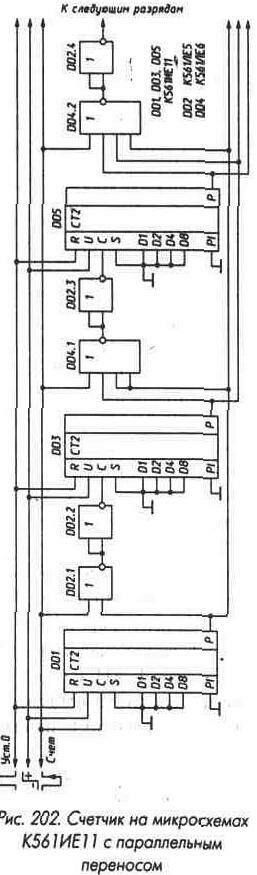

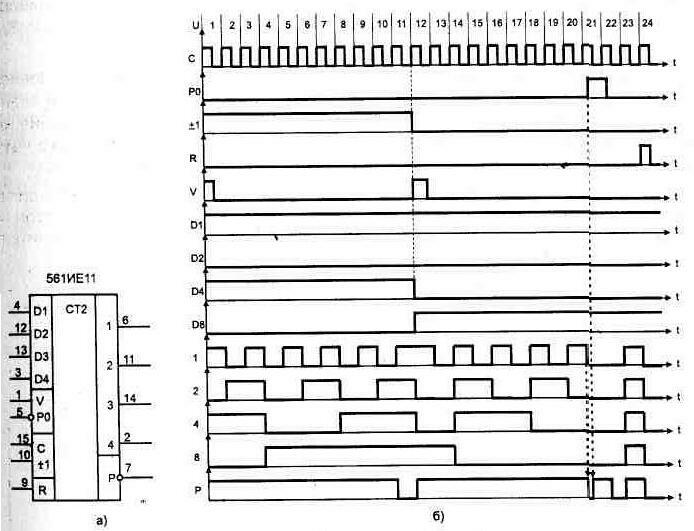

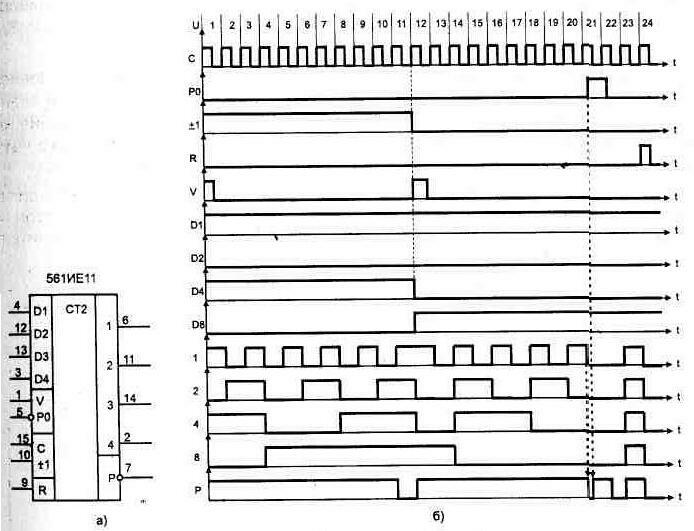

МикросхемаИЕ11 - десятичный синхронный счетчик (рис. 38). Логика его работы соответствует логике работы счетчиков ИЕ9. Отличие лишь в том, что для сброса в состояние 0 счетчика ИЕ9 необходима подача на вход R лог. 0, а для сброса в состояние 0 счетчика ИЕ11 кроме подачи на вход ER (разрешение уст. 0) лог. 0

необходима подача тактового импульса отрицательной полярности на вход С, по спаду которого и происходит сброс счетчика. Таким образом, все изменения выходных сигналов этой микросхемы происходят по спаду импульсов отрицательной полярности на входе С.

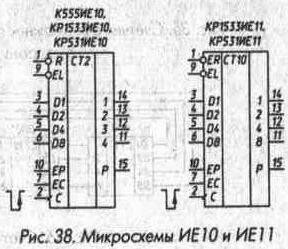

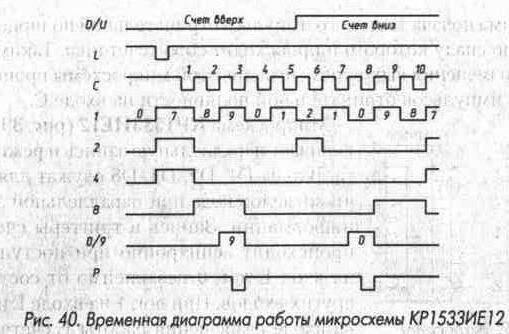

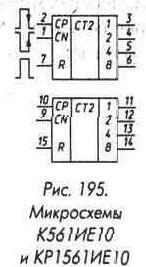

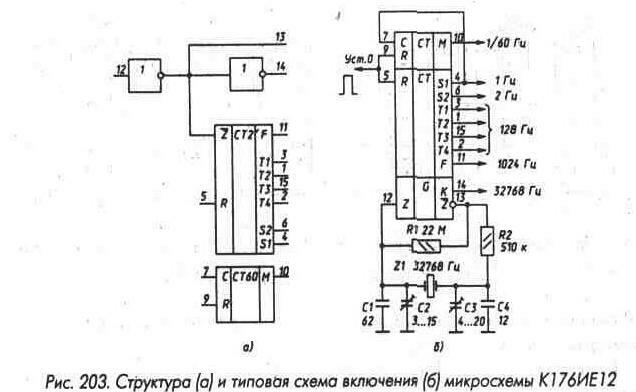

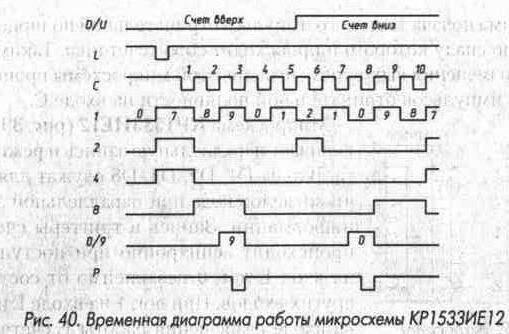

МикросхемаКР1533ИЕ12 (рис. 39) обеспечивает параллельную запись и режим счета. Входы Dl, D2, D4, D8 служат для подачи сигналов кода при параллельной записи информации. Запись в триггеры счетчика происходит асинхронно при поступлении на вход L лог. 0 независимо от состояния других входов. При лог. 1 на входе L и лог. 0 на входе разрешения работы Е счетчик изменяет состояние по спадам импульсов отрицательной полярности на входе С. На

правление счета определяется сигналом на входе D/U: при лог. 0 происходит счет вверх, при лог. 1 - вниз.

Для построения многоразрядных счетчиков у микросхемы есть два специальных выхода: последнего состояния 0/9 и переноса Р. На выходе 0/9 лог. 1 появляется при достижении состояния 9 при прямом счете и состояния 0 при обратном. В остальных случаях на выходе 0/9 - лог. 0. При наличии лог. 1 на выходе 0/9 и лог. 0 на входе Е одновременно с импульсом на входе С на выходе переноса Р появляется импульс отрицательной полярности и той же длительности.

Счетчик КР1533ИЕ12 не имеет входа установки в 0. Для этой цели на входы Dl, D2, D4, D8 подают лог. 0, а на вход L - импульс отрицательной полярности. Смена сигналов на входах D/U и Е должна происходить в момент переключения сигнала на входе С из лог. 0 в лог. 1 или в паузе между импульсами на входе С (то есть при лог. 1 на этом входе).

Пример временной диаграммы работы счетчика представлен на рис. 40. По импульсу отрицательной полярности на входе L записываются сигналы кода числа 7 в триггеры счетчика (сигналы кода 0111 на входах D8, D4, D2, Dl не показаны). Первые пять импульсов на входе С переводят его последовательно в состояния 8, 9, 0, 1, 2. На выходе 0/9 лог. 1 появляется при переходе счетчика в состояние 9. Импульс на его выходе Р формируется одновременно с третьим импульсом на входе С, по спаду которого счетчик переключается в состояние 0.

В момент окончания пятого импульса происходит смена направления счета изменением сигнала на входе D/U и следующие пять импульсов на входе С переводят счетчик последовательно в состояния 1, 0, 9,

8,7 и т. д. При переходе счетчика в состояние 0 на выходе 0/9 появляется лог. 1, а одновременно с восьмым импульсом на входе С, переключающим счетчик в состояние 9, на выходе Р формируется импульс отрицательной полярности.

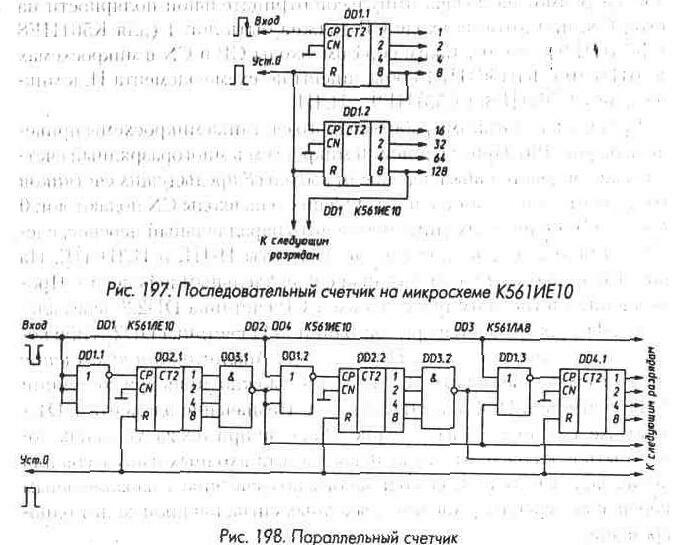

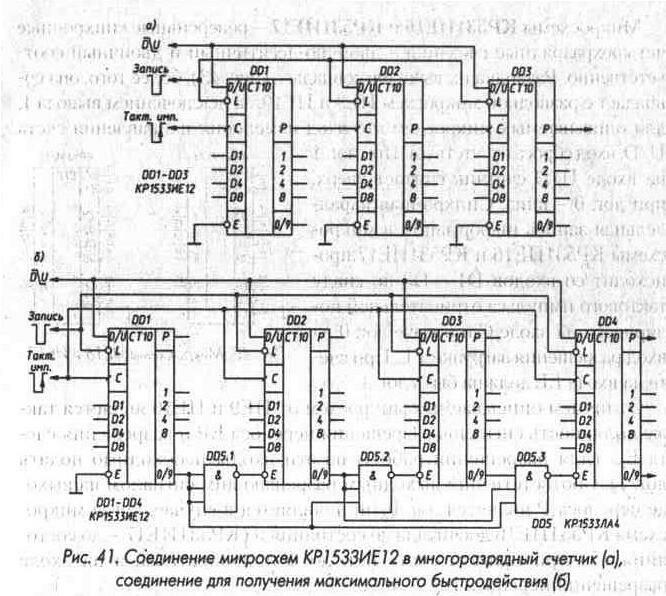

Схема соединения микросхем КР1533ИЕ12 в многоразрядный счетчик показана на рис. 41 (а). Из-за последовательного переключения быстродействие такого счетчика в реверсивном режиме снижается относительно быстродействия одной микросхемы.

Если необходим реверсивный счетчик с максимально возможным быстродействием, его собирают по схеме рис. 41 (б). В этом счетчике все триггеры микросхем переключаются одновременно и его быстродействие не зависит от числа разрядов. Однако для каждого десятичного разряда, кроме первого, требуется элемент И-НЕ с числом входов, возрастающим по мере роста номера разряда.

В зависимости от необходимого быстродействия возможно построение различных вариантов последовательно-параллельного счетчика. Можно, например, не использовать выход 0/9 микросхемы DD4 (рис. 41, б), а ее выход Р соединить с входом тактовых импульсов второго такого счетчика.

МикросхемаКР1533ИЕ13 (рис. 39) аналогична КР1533ИЕ12, но ее коэффициент пересчета равен 16. Все правила ее использования и схемы включения соответствуют микросхеме КР1533ИЕ12.

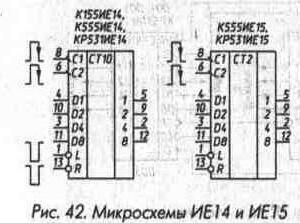

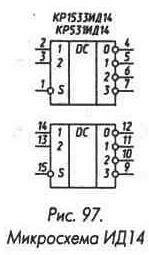

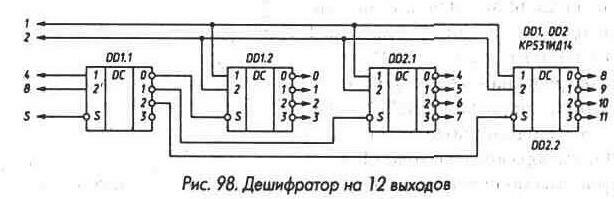

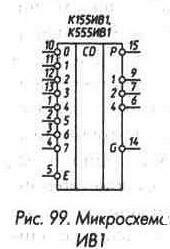

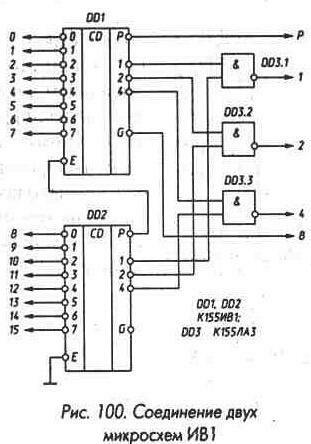

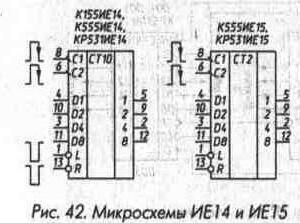

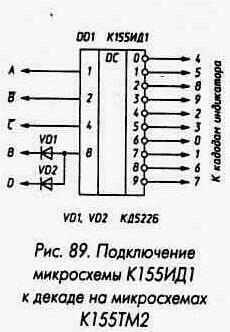

МикросхемаИЕ14 (рис. 42) во многом напоминает микросхему ИЕ2. Она также содержит счетный триггер с входом С2. При соединении выхода 1 счетного триггера (вывод 5) с входом С2 образуется двоично-десятичный счетчик, работающий в коде 1-2-4-8. Срабатывание триггера и делителя на 5 происходит по спадам импульсов положительной

полярности. Различие с микросхемой ИЕ2 заключается в полярности импульсов сброса - триггеры микросхемы ИЕ14 устанавливаются в 0 при подаче на вход R лог. 0. Кроме того, в микросхеме ИЕ14 есть возможность предварительной установки триггеров счетчика. Для установки триггеров необходимый код следует подать на входы D1 - D8, а на вход L - импульс отрицательной полярности. При лог. 0 на входе L сигналы на выходах 1-8 повторяют сигналы на входах D1 - D8, при лог. 1 происходит запоминание и возможен счетный режим работы микросхемы.

Микросхему можно использовать в счетчиках с предварительной установкой, например, в цифровых шкалах радиоприемников и трансиверов с учетом промежуточной частоты.

МикросхемаИЕ15 (рис. 42) по своей структуре и функционированию аналогична микросхеме ИЕ14, но делитель с входом С2 делит частоту на 8,

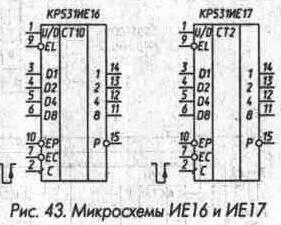

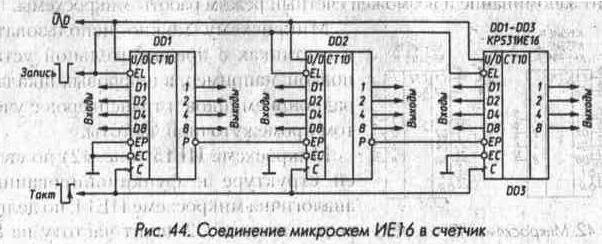

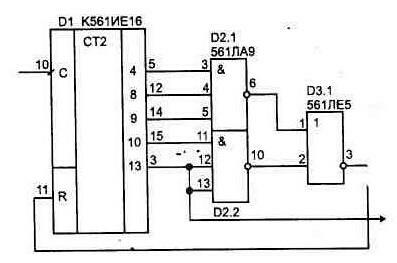

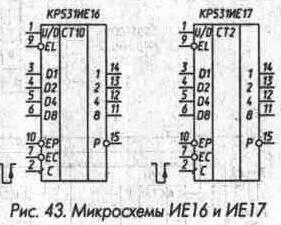

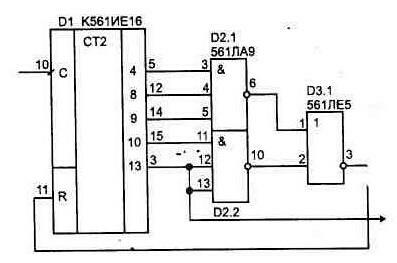

Микросхемы КР531ИЕ16 иКР531ИЕ17 - реверсивные синхронные четырехразрядные счетчики - двоично-десятичный и двоичный соответственно. Разводка их выходов совпадает (рис. 43), более того, она совпадает с разводкой микросхем ИЕ9 и ИЕ10, за исключением вывода 1, для описываемых микросхем это вход изменения направления счета

U/D, вход сброса отсутствует. При лог. 1 на входе U/D счетчик считает вверх, при лог. 0 - вниз. Синхронная параллельная запись информации в микросхемы КР531ИЕ16 и КР531ИЕ17 происходит со входов D1 - D8 по спаду тактового импульса отрицательной полярности на входе С и подаче лог. 0 на вход разрешения загрузки EL. При счете на входе EL должна быть лог. 1.

Отличием описываемых микросхем от ИЕ9 и ИЕ10 является также полярность сигналов разрешения переноса ЕР и разрешения счета ЕС (для разрешения работы на эти входы необходимо подать лог. 1). Соответственно выходным разрешающим сигналом на выходе переноса Р является лог. 0, он появляется в случае, когда микросхема КР531ИЕ16 досчитала до состояния 9 (КР531ИЕ17 - до состояния 15) при прямом счете или до 0 при обратном, а на входе разрешения переноса ЕР - лог. 0.

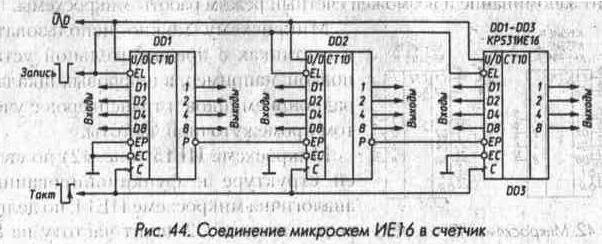

Примеры соединения микросхем КР531ИЕ16 и КР531ИЕ17 в многоразрядный счетчик приведены на рис. 44 и 45. При соединении микросхем по схеме рис. 44 максимальная частота счета снижается по отношению к максимально возможной для одной микросхемы, при соединении по схеме рис. 45 - не снижается. Следует помнить, что переключение направления счета на входе U/D и смену информации на входах ЕР и ЕС следует производить в паузе между

тактовыми импульсами, то есть при лог. 1 на входах С микросхем или в момент изменения сигнала на этих входах с лог. 0 на лог. 1. Входной ток микросхем по входу ЕР в состоянии лог. 0-4 мА. МикросхемаИЕ18 (рис. 46) аналогична по функционированию микросхеме ИЕ11, но ее коэффициент пересчета равен 16.

Рассмотренные выше микросхемы счетчиков серии КР531 имеют входные токи по управляющим входам, как правило, больше стандартных. При подаче на входы лог. 0 токи составляют для микросхем КР531ИЕ9 и КР531ИЕ10 по выводу 2 - 5 мА, выводу 10-3 мА, выводу 9-4 мА. Для микросхем КР531ИЕ11 и КР531ИЕ18 ток по вы

воду 10 составляет 4 мА, а для КР531ИЕ14 и КР531ИЕ15 ток по выводу 8-8 мА, по выводу 6-10 мА, по выводам 1, 3, 4, 10, 11, 13 - 0,75 мА.

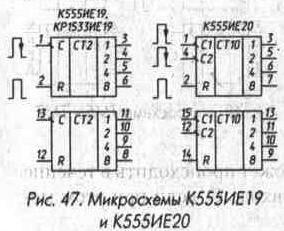

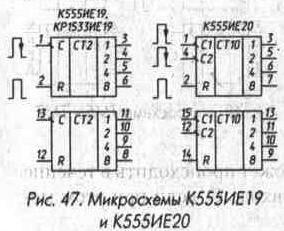

МикросхемаК555ИЕ19 - два четырехразрядных двоичных счетчика (рис. 47), каждый из которых имеет два входа: R - для установки триггеров счетчика в 0 при подаче на вход R лог. 1 и С - для подачи счетных импульсов. Срабатывание триггеров счетчика происходит по спадам импульсов положительной полярности, подаваемых на вход С,

выходной код счетчиков - стандартный, 1-2-4-8. Для соединения счетчиков в многоразрядный выходы 8 предыдущих разрядов необходимо соединить со входами С последующих.

МикросхемаК555ИЕ20 (рис. 47) -два четырехразрядных двоично-десятичных счетчика, каждый из которых аналогичен счетчику микросхем ИЕ2, за исключением входов установки в 0 R.

Каждый счетчик имеет триггер со входом С1, выходом 1 и делитель частоты на 5 со входом С2 и выходами 2,4,8. Триггер и счетчик срабатывают по спадам положительных импульсов, подаваемых на входы С1 и С2, на входе R при счете должен быть лог. 0. Для получения десятичного счетчика выход 1 надо соединить со входом С2, при этом код счетчика будет 1-2-4-8. Если же выход 8 соединить со входом С1, входные импульсы подать на вход С2, выходной код будет 1-2-4-5, а на выходе 1 сигнал будет иметь форму меандра с частотой, в 10 раз меньше входной. Впрочем, так же можно соединять счетчики микросхем ИЕ2 и ИЕ14. Предельная частота работы триггера - 25 МГц, делителя на 5 - 20 МГц.

Рис. 24 Микросхема К155ИЕ1

Рис. 25 Микросхемы К155ИЕ2, К155ИЕ4, К155ИЕ5

Рис. 26 Делитель частоты на 10 на микросхеме К155ИЕ4 и диаграмма его работы

Рис. 27 Декада на микросхеме К155ИЕ4 с возможностью установки в 0

Рис. 28 Микросхемы ИЕ6 и ИЕ7

Рис. 29 Временная диаграмма работы микросхемы ИЕ6

Рис. 30 Микросхема К155ИЕ8

Рис. 31 Временная диаграмма работы микросхемы К155ИЕ8

Рис. 32 Схема соединения двух делителей К155ИЕ8

Рис. 33 Микросхема ИЕ9

Рис. 34 Соединение микросхем ИЕ9 в счетчик, соединение для получения максимального быстродействия

Рис. 35 Счетчик с возможностью сдвига в сторону старших разрядов

Рис. 37 Делитель с управляемым коэффициентом деления

Рис. 38 Микросхемы ИЕ10 и ИЕ11

Рис. 39 Микросхемы КР1533ИЕ12 и КР1533ИЕ13

Рис. 40 Временная диаграмма работы микросхемы КР1533ИЕ12

Рис. 41 Соединение микросхем КР1533ИЕ12 в многоразядный счетчик

Рис. 42 Микросхемы ИЕ14 и ИЕ15

Рис. 43 Микросхемы ИЕ16 и ИЕ17

Рис. 44 Соединение микросхем ИЕ16 в счетчик

Рис. 45 Соединение микросхем ИЕ16 в счетчик для получения максимального быстродействия

Рис. 46 Микросхема ИЕ18

Рис. 47 Микросхемы К555ИЕ19 и К555ИЕ20

Ф.1 Определение коэффициента пересчета

1.3.3 Регистры.

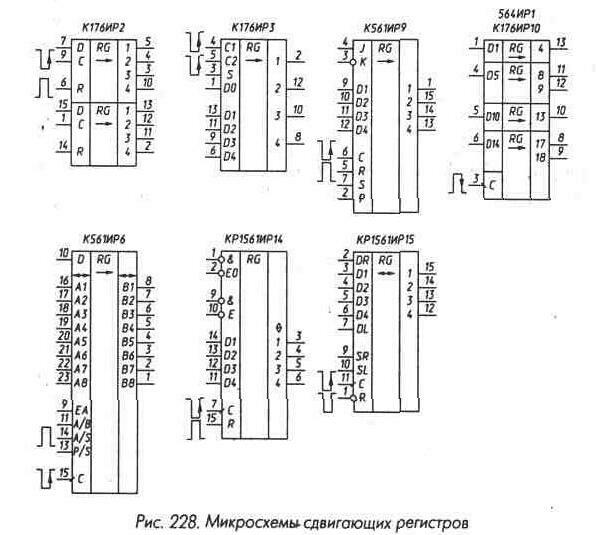

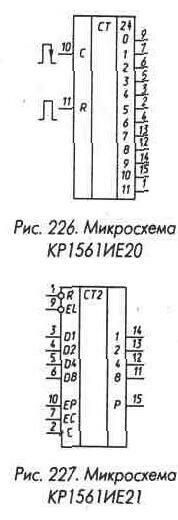

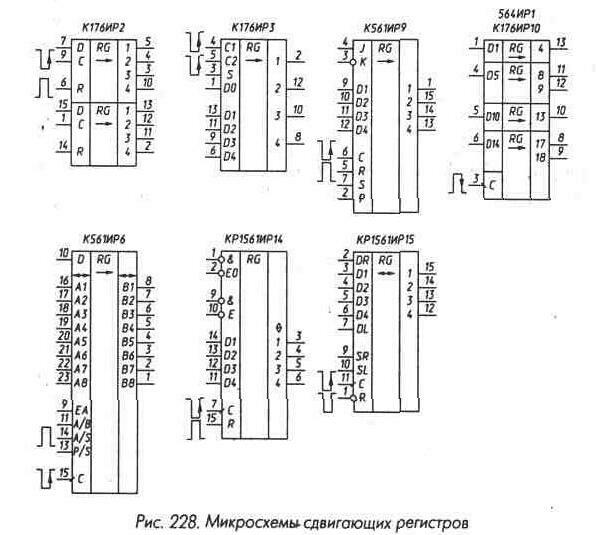

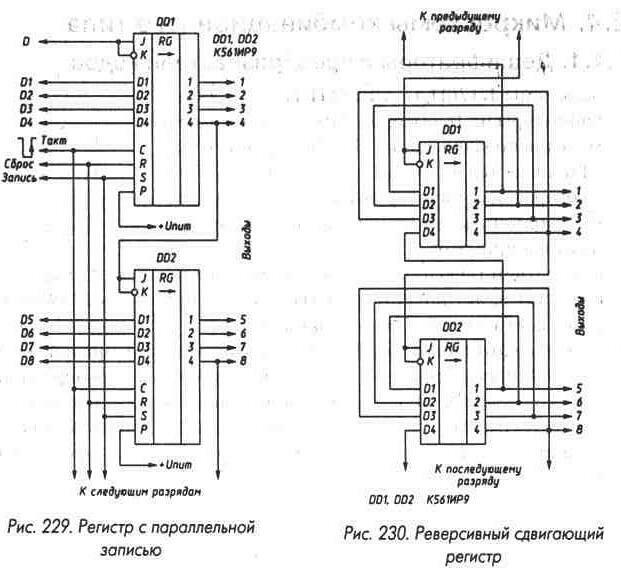

1.3.3. Регистры

Регистры можно разделить на два класса - сдвигающие и хранения информации. В свою очередь, регистры хранения бывают «прозрачные», тактируемые импульсом, и синхронные, тактируемые фронтом импульса.

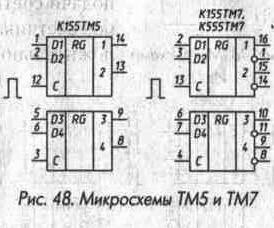

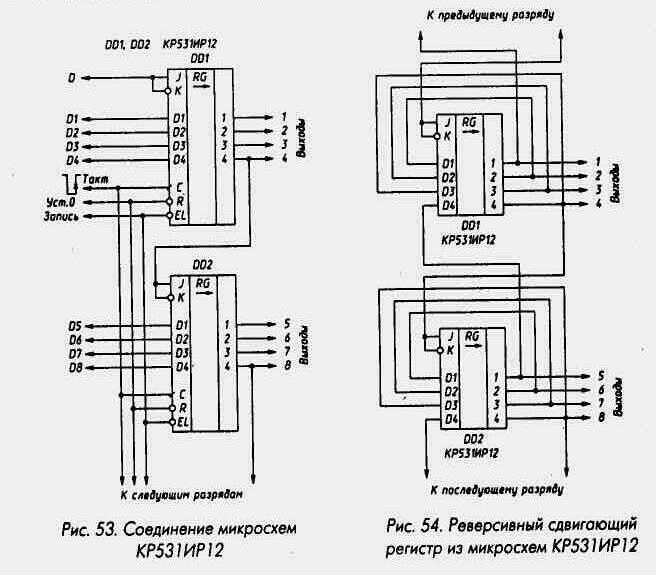

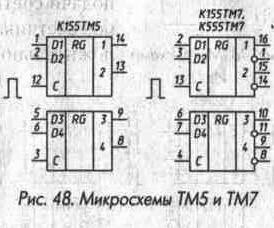

МикросхемыК155ТМ5 и ТМ7 (рис. 48) содержат по четыре триггера, образующих два двухразрядных регистра хранения информации. Каждый триггер имеет информационный вход D, тактовый вход С и прямой выход (а в микросхеме ТМ7 еще и инверсный выход). Триггер работает следующим образом. При лог. 0 на входе С изменение сигнала на входе D не влияет на состояние триггера и он хранит записанную в нем ранее информацию. При подаче на вход С лог. 1 триггер превращается в повторитель - сигнал на выходе соответствует сигналу на входе, за это свойство подобные триггеры называют «прозрачными». При подаче на вход С лог. 0 триггер переходит вновь в режим хранения, а его состояние определяется сигналом на входе D перед спа-

дом импульса на входе С. Таким образом, основные свойства триггеров микросхем К155ТМ5 и ТМ7 следующие:

1) при подаче на вход С лог. 0 - хранение информации;

2) при подаче на вход С лог. 1 - повторение входного сигнала;

3) запоминается информация, имеющаяся на входе D перед спадом на входе С;

4) изменение информации на выходе может происходить в течение всего положительного импульса на входе С, если при этом меняется информация на входе D.

Эту разновидность D-триггера называют «D-триггером, тактируемым импульсом», «триггером-защелкой», «прозрачным» триггером, чтобы отличать ее от описанных выше D-триггеров ТМ2, которые можно назвать «D-триггерами, тактируемыми фронтом» или «синхронными D-триггерами».

Для того чтобы подчеркнуть различие между ними, приведем логику работы D-триггера, тактируемого фронтом импульса:

1) хранение информации осуществляется при подаче на вход С как лог. 0, так и лог. 1;

2) прямое прохождение сигнала на выход со входа D нет;

3) запоминается информация, имеющаяся на входе D перед фронтом импульса положительной полярности на входе С;

4) изменение информации на выходе может происходить только во

время фронта на входе С.

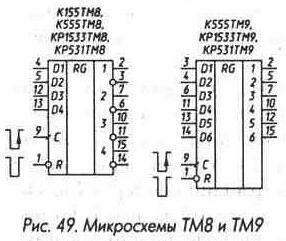

МикросхемаТМ8 (рис. 49) - регистр хранения информации, содержащий четыре синхронных D-триггера, по функционированию анало

гичных триггерам микросхем ТМ2. Сброс триггеров происходит при подаче лог. 0 на вход R, запись - по спаду импульса отрицательной полярности на входе С. Информация на входах D1 - D4 может меняться как при лог. 0, так и при лог. 1 на входе С, она важна лишь непосредственно перед изменением сигнала на входе С с лог. 0 на лог. 1. МикросхемаТМ9 - регистр хране

ния информации, содержащий шесть D-триггеров, по функционированию аналогичных триггерам микросхем ТМ2 и ТМ8.

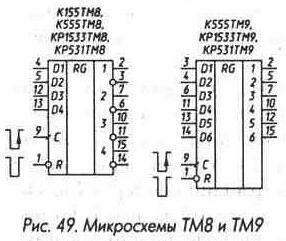

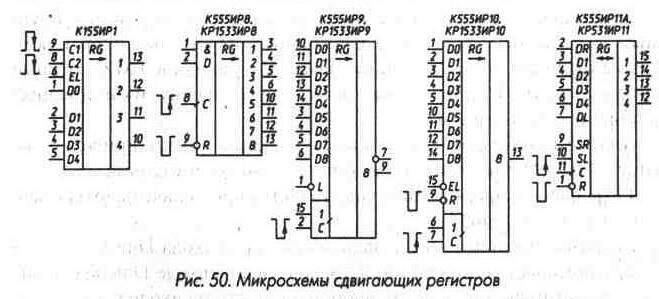

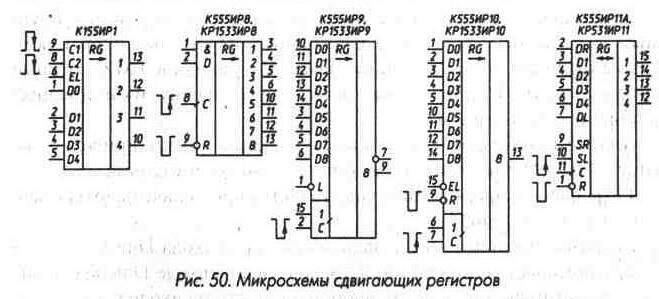

МикросхемаК155ИР1 (рис. 50) - четырехразрядный сдвигающий регистр, позволяет производить последовательную и параллельную запись информации в триггеры регистра, последовательное и параллельное считывание информации, сдвиг информации. Вход С1 микросхемы служит для подачи положительных тактовых импульсов, сдвигающих информацию, причем сдвиг происходит по спадам импульсов. При подаче положительного импульса на вход С2 по его спаду происходит запись в триггеры регистра информации, имеющейся на входах D1 - D4. Кроме того, есть управляющий вход EL. Запись со входов D1 - D4 может происходить лишь при наличии лог. 1 на входе EL, сдвиг - при наличии лог. 0. Для последовательной записи информации используется вход D0, запись происходит в режиме сдвига.

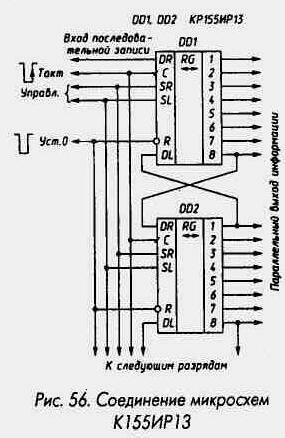

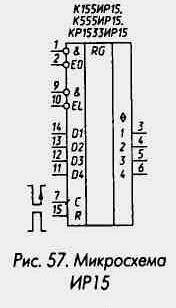

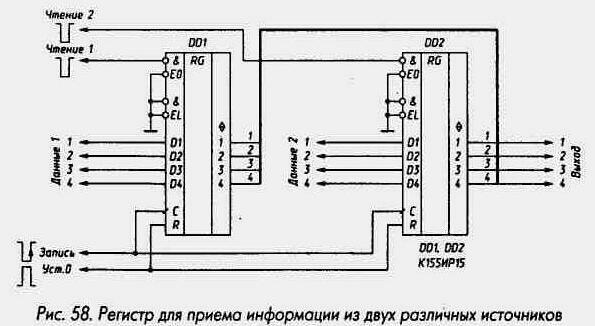

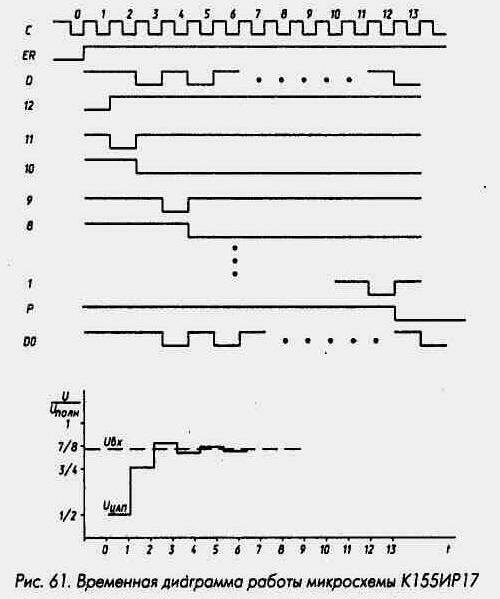

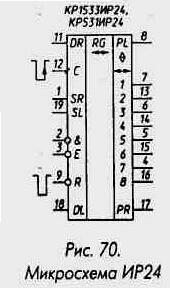

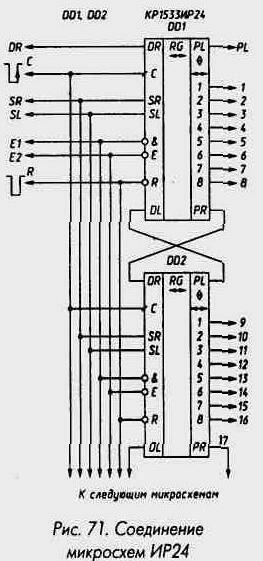

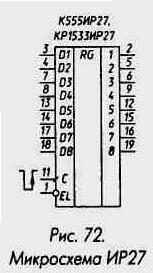

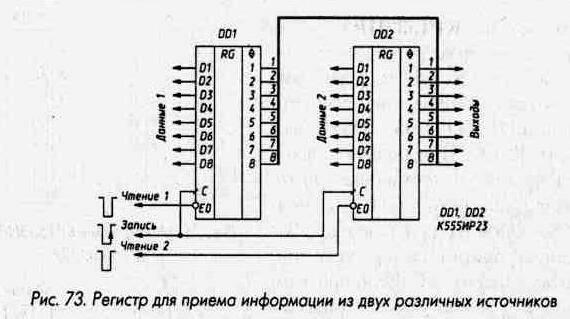

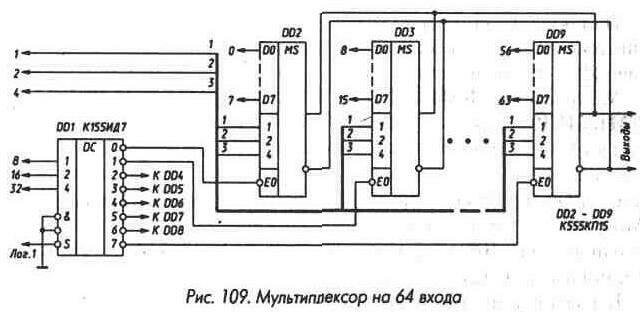

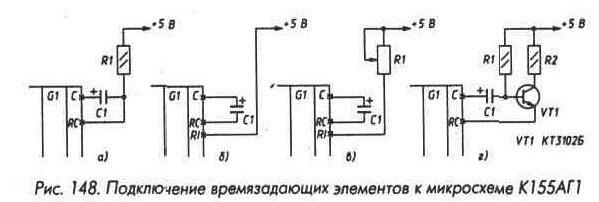

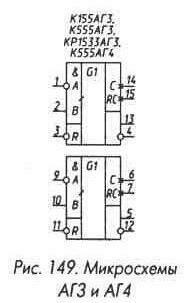

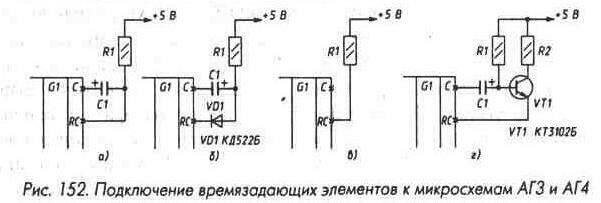

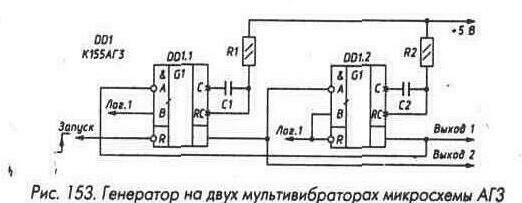

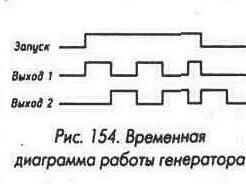

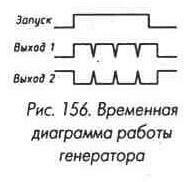

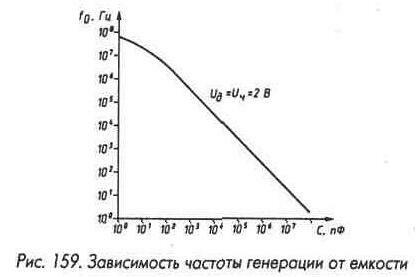

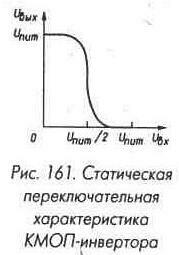

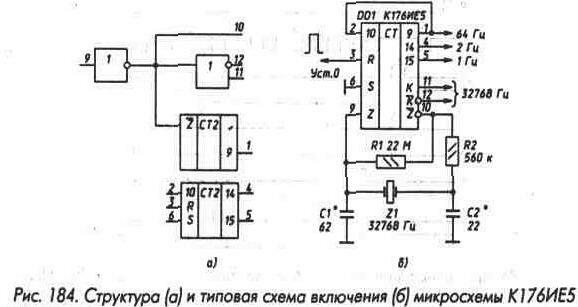

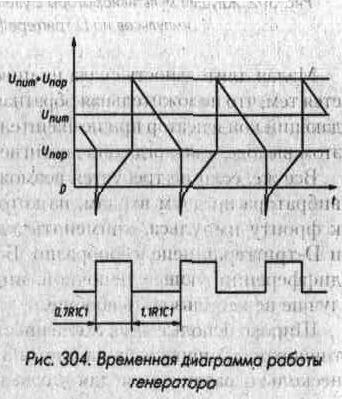

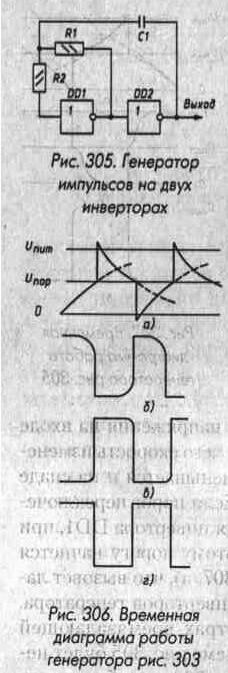

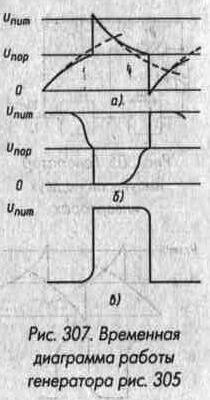

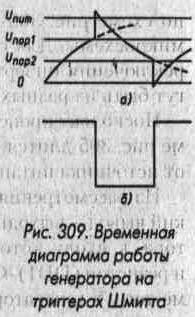

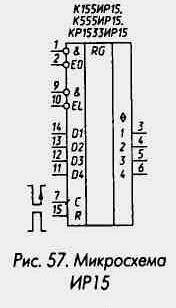

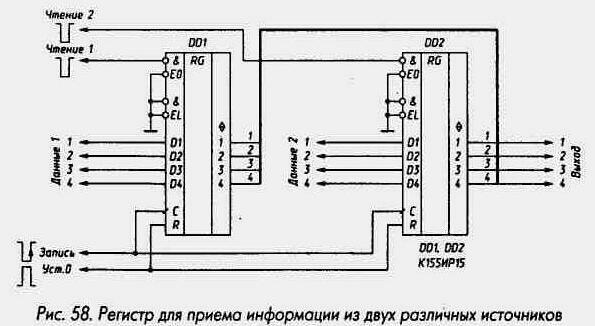

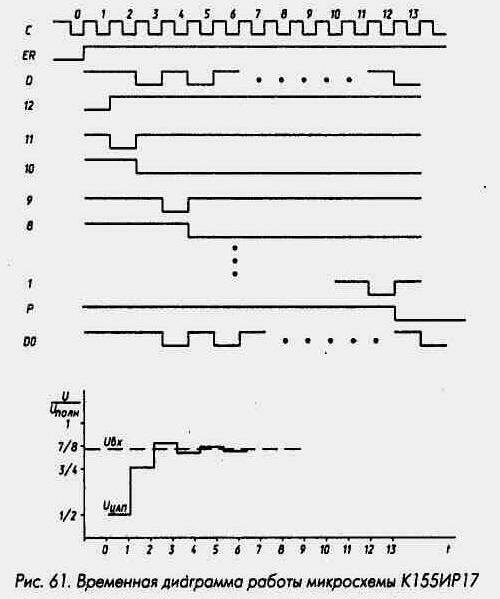

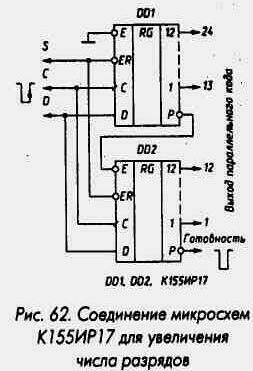

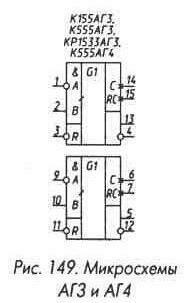

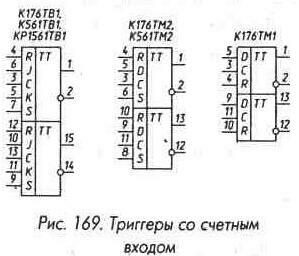

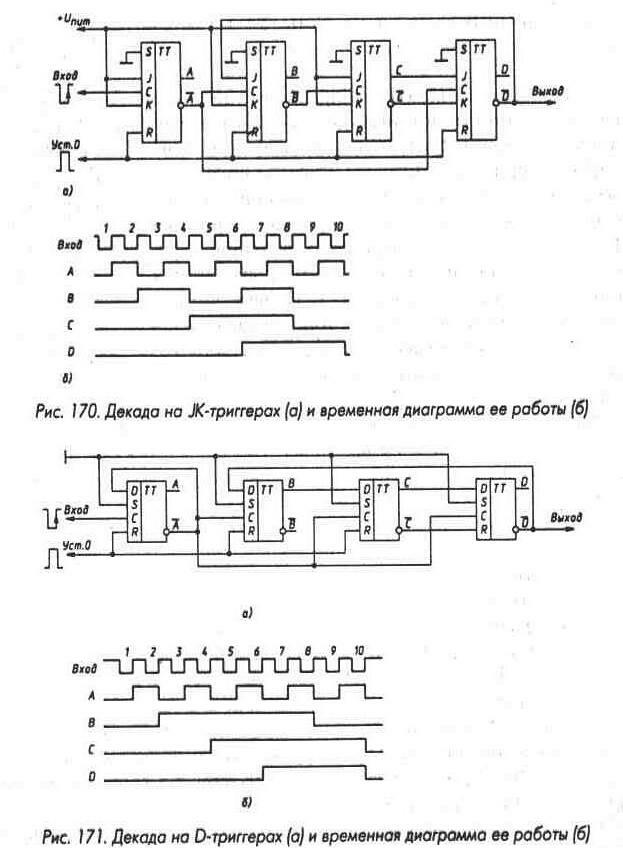

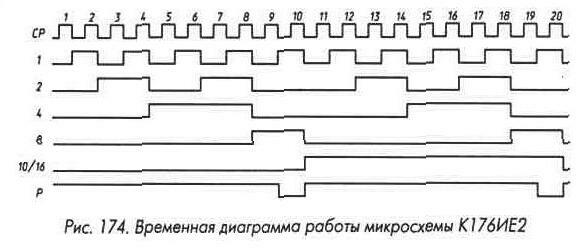

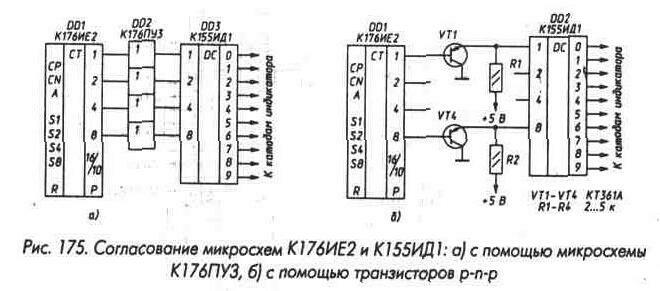

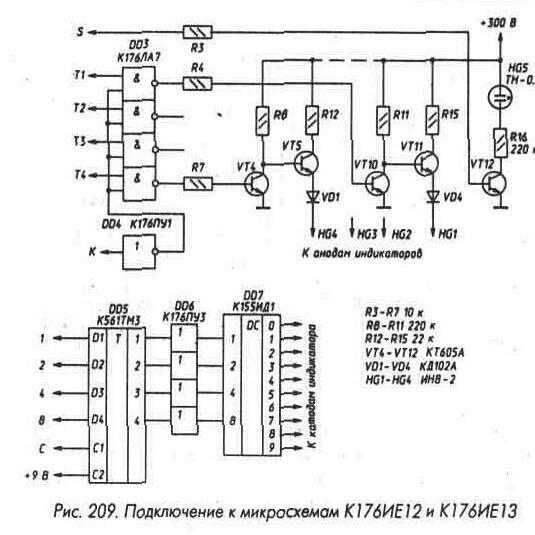

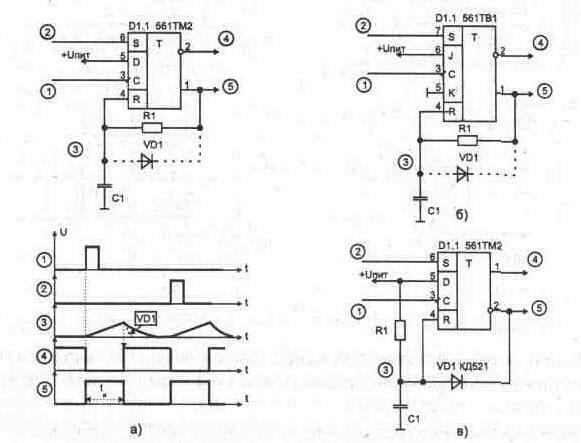

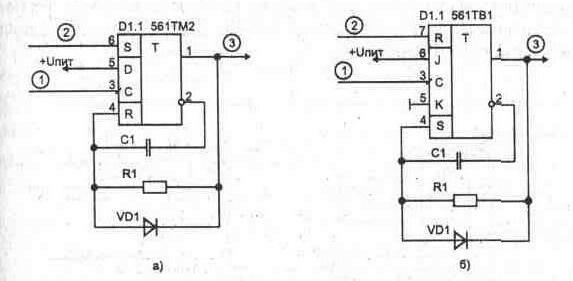

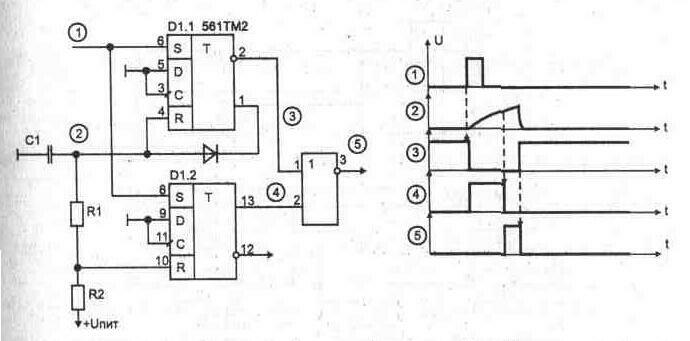

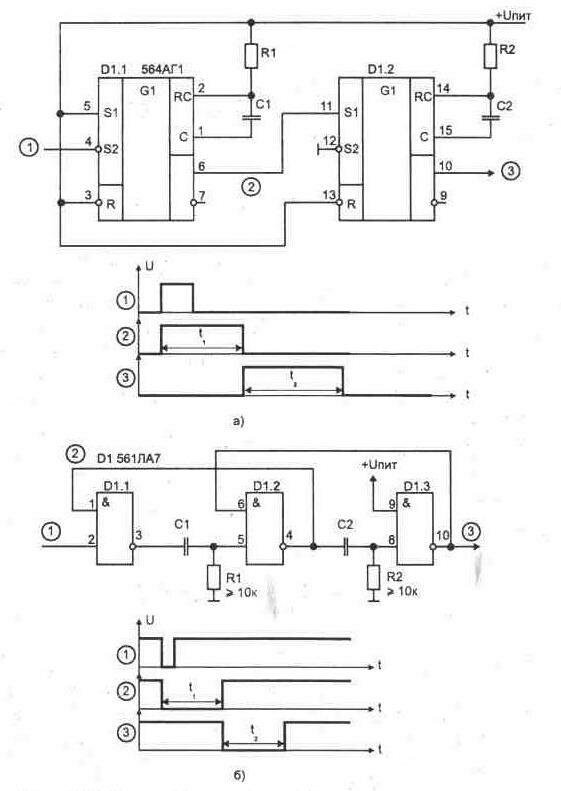

Наличие управляющего входа EL расширяет возможности использования микросхемы. Если соединить между собой входы С1 и С2, можно управлять сдвигом и записью, лишь изменяя логический уровень на входе EL. Можно соединить между собой входы С2 и EL, специального управляющего сигнала в этом случае не потребуется -сдвиг будет происходить при подаче импульсов на вход С1, запись -при подаче импульсов на С2.