2.4.3 Сумматоры и другие элементы.

2.4.3. Сумматоры и другие элементы

МикросхемыК176ИМ1 и К561ИМ1 (рис. 262) -полные четырехразрядные сумматоры. На входы А1 - А4 подается код одного из суммируемых чисел (А1 - младший разряд), на входы В1 - В4 -код второго числа, на вход С - перенос от предыдущей микросхемы. На выходах SI - S4 формируется код суммы чисел, на выходе Р - сигнал переноса в следующую микросхему. В микросхеме, суммирующей младшие разряды многоразрядного двоичного числа, вход С соединяют с общим проводом.

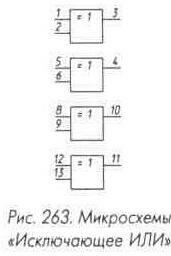

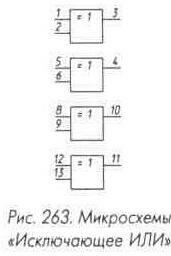

МикросхемыК176ЛП2, К561ЛП2 и КР1561ЛП14 содержат по четыре двухвходовых элемента «Исключающее ИЛИ» (рис. 263), которые также являются сумматорами по модулю два.

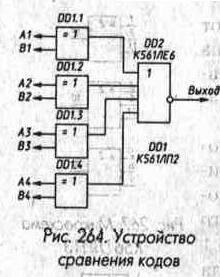

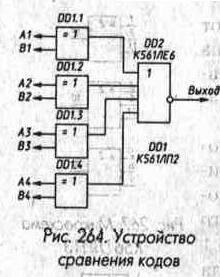

Часто микросхемы, выполняющие функции «Исключающее ИЛИ», используют для сравнения на равенство двоичных кодов, поступающих от различных источников. Для примера на рис. 264 приведена схема устройства сравнения двух четырехразрядных кодов А1 - А4 и В1 - В4. При равенстве кодов на всех выходах микросхемы DD1 появляются лог. 0 и на выходе DD2 -лог. 1. При различии кодов хотя бы в одном разряде на соответствующем выходе микросхемы DD1 появляется лог. 1, а на выходе DD2 - лог. 0.

Если в качестве DD2 использовать элемент И-НЕ, один из входных кодов нужно подать в инверсном виде.

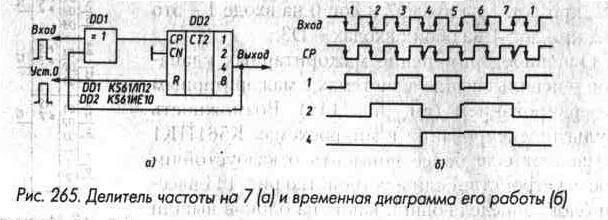

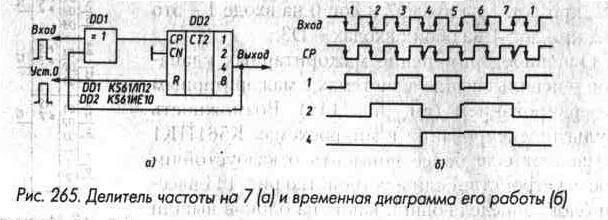

Интересно применение микросхем «Исключающее ИЛИ» для изменения коэффициента деления счетчиков. Если перед подачей тактовых импульсов на счетный вход счетчика их пропустить через элемент «Исключающее ИЛИ», на второй вход которого подать сигнал с выхода этого счетчика, коэффициент деления уменьшается на единицу. Для примера на рис. 265 (а) приведена схема делителя частоты

на семь, полученного указанным способом, а на рис. 265 (6) - временная диаграмма его работы. На выходе 4 микросхемы DD2 частота импульсов меньше входной в 7 раз, а на выходе 2 - в 3,5 раза при сохранении периодичности. Интересно отметить, что если исходный счетчик имел скважность выходных импульсов, равную двум, и на вход делителя также подается меандр, на выходе получается меандр, как это имеет место для приведенной схемы.

МикросхемаК561СА1 - сумматор по модулю два на тринадцать входов (рис. 266). Выходной сигнал микросхемы принимает значение лог. 1 при нечетном числе входов, на которые поданы лог. 1, и лог. 0 в противном случае. Задержка распространения сигнала по входу 10 меньше, чем по другим входам, поэтому его используют для расширения, подключая к нему выход другой такой же микросхемы.

МикросхемаК561ЛП13 содержит три трехвходовых мажоритарных клапана (рис. 267). Выходной сигнал мажоритарного клапана соответствует входным сигналам на большинстве входов, то есть

если лог. 1 присутствует на двух или трех входах, на выходе - лог. 1, если лог. 1 только на одном входе или на всех входах лог. 0, на выходе - лог. 0. Подав на один из входов мажоритарного клапана лог. 0, получаем двухвходовый неинвертирующий элемент И, подав лог. 1, получаем элемент ИЛИ. Повторитель можно получить, объединив все три входа или подав на один вход лог. 1, на другой - лог. 0.

МикросхемаК561ИК1 - три элемента, которые могут работать в двух режимах - как мажоритарные клапаны и как мультиплексоры

на три входа (рис. 268). Все три элемента имеют два общих управляющих входа, обозначенных на рис. 268 цифрами 1 и 2. При подаче на оба управляющих входа лог. 0 элементы работают как мажоритарные клапаны микросхемы К561ЛПЗ.

Если же хотя бы на одном из управляющих входов лог. 1, элементы выполняют функции мультиплексоров. Выходной сигнал мультиплексора соответствует сигналу входа, номер которого в двоичном коде подан на входы 1 и 2. При лог. 1 на входе 1 и лог. 0 на входе 2 это сигнал со входа D1, при лог. 1 на входе 2 и лог. 0 на входе 1 - это D2, при лог. 1 на обоих входах - D3.

Основное применение мажоритарных клапанов - использование в системах с мажоритарным резервированием (см. рис. 144). Возможность мультиплексирования в микросхемах К561ИК1 позволяет еще более повысить отказоустойчивость устройств. Если в устройство рис. 144 ввести блок, определяющий, какие из блоков вышли из строя, можно сохранить работоспособность устройства в целом даже при выходе из строя большинства блоков. Например, если выйдут из строя блоки DD1, DD2, DD6, DD7, а блок управления, определив это, выдаст на микросхему DD4 типа К561ИК1 код 11, на DD8 - 10, на блоки DD5 - DD7 поступят сигналы с исправного блока DD3, на DD9 - DD11 - с DD5 и устройство сохранит работоспособность в целом.

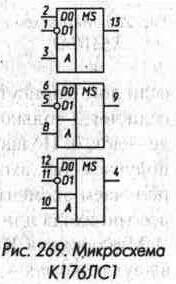

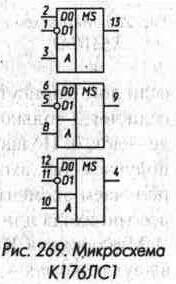

МикросхемаК176ЛС1 - три двухвходовых независимых мультиплексора (рис. 269). Если на управляющий вход А мультиплексора

подать лог. 0, на выход проходит сигнал со входа DO, если лог. 1 - на выходе инверсия сигнала со входа D1. Если объединить между собой входы D0 и D1, получится элемент «Исключающее ИЛИ». При подаче лог. 0 на вход D1 два оставшихся входа образуют входы элемента ИЛИ. Подав на входы А и D1 лог. 0, получим неинвертирующий логический элемент с одним входом DO. Аналогично, подав лог. 1 на входы А и D0, получим инвертор со входом D1. Такая гибкость микросхемы К176ЛС1 позволяет широко использовать ее в различных схемах.

МикросхемаК561ЛС2 - четыре элемента ИЛИ-НЕ с общими входами стробирования (рис. 270). Наиболее распространенное ее применение - мультиплексирование двух четырехразрядных источников цифрового сигнала. Если на управляющий вход 9 подать лог. 1, на вход 14 -лог. 0, на выходы 13, 12, 11, 10 пройдут сигналы со входов 15, 2, 4 и 6. Если лог. 1 подать на вход 14, лог. 0 - на вход 9, на выходы поступят сигналы со входов 1, 3, 5, 7. Если же лог. 1 подать на оба управляющих входа 9 и 14, микросхема превратится в четыре независимых неинвертирующих элемента ИЛИ.

МикросхемаК561ИП2 (рис. 271) служит для сравнения двух четырехразрядных двоичных или двоично-десятичных чисел. Она имеет четыре входа А1 - А8 для подачи кода первого числа, четыре входа В1 - В8 для подачи кода второго числа, входы переноса >, =, < и выходы переноса, обозначаемые аналогично.

Вход переноса > (вывод 4) избыточен, и для нормальной работы микросхемы на него должна постоянно подаваться лог. 1. Если используется одна микросхема К561ИП2, на ее входы = и < сле-дует подать соответственно лог. 1 и лог. 0. На вы-

ходе > появится лог. 1, если число А, код которого подан на входы А1 - А8, больше числа В, код которого подан на входы В1 - В8. На выходе = лог. 1 появится при равенстве чисел А и В, на выходе < -если число А меньше В. При этом на других выходах будет лог. 0.

Для обеспечения сравнения чисел с большим числом разрядов микросхемы следует соединять между собой так, как это показано на рис. 272. Старшие разряды сравниваемых кодов следует подавать на микросхему DD3, младшие - на DD1.

Микросхемы К561ИП2 могут использоваться в устройствах поиска записей в магнитофонах, для цифровой автоподстройки частоты, в делителях с переключаемым коэффициентом деления, в будильниках и во многих других случаях.

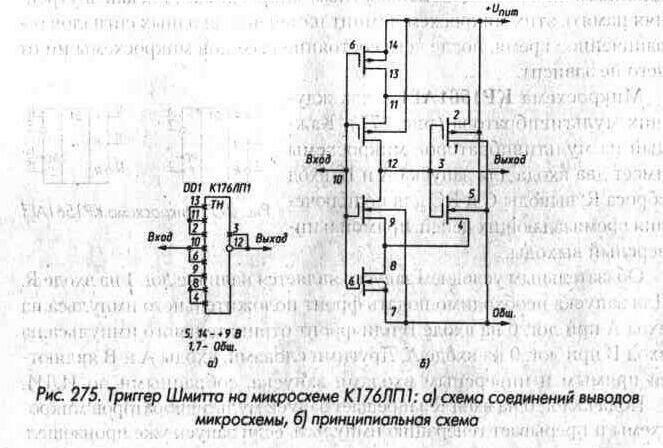

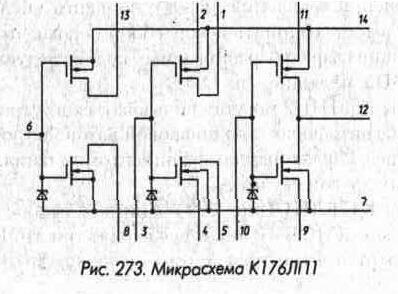

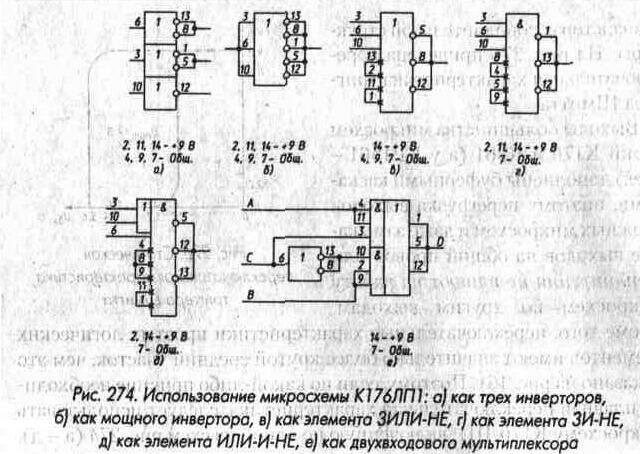

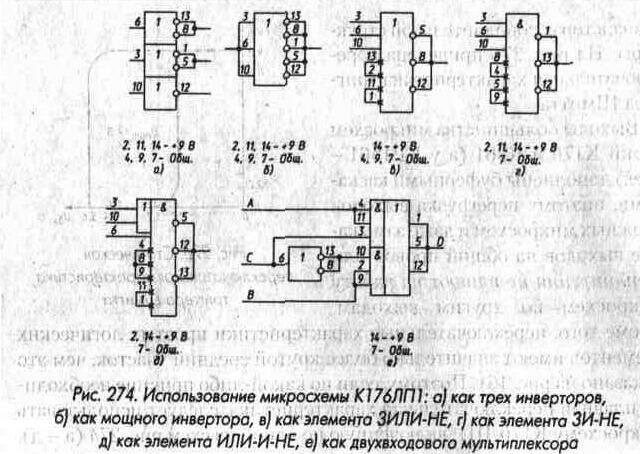

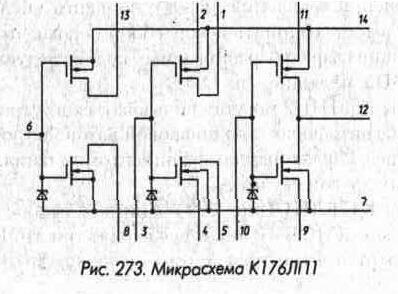

Микросхема К176ЛП1 (рис. 273) занимает особое место среди других микросхем КМОП-серий. В нее входят три МОП-транзистора с каналом р-типа и три транзистора с каналом n-типа, частично

соединенные между собой. Путем внешних соединений из этой мик-росхемы можно получить три отдельных инвертора (рис. 274, а), ин-вертор с мощным выходом (рис. 274, б), трехвходовый элемент ИЛИ-НЕ (рис. 274, в), трехвходовый элемент И-НЕ (рис. 274, г), элемент ИЛИ-И-НЕ, отсутствующий в КМОП-сериях микросхем (рис. 274, д), мультиплексор на два входа (рис. 274, е).

Мультиплексор по схеме рис. 274 (е) пропускает сигнал со входа А на выход D при лог. 1 на входе С, и со входа В на выход D при лог. 0 на входе С. Мультиплексор обратим - при подаче входного сигнала на выход D он будет проходить на вход А при лог. 1 на входе С и на вход В при лог. 0 на входе С.

Так же, как и для ключей К176КТ1, К561КТЗ и КР1561КТЗ, про-пускаемый сигнал может быть цифровым или аналоговым и не дол-жен выходить за пределы напряжения питания.

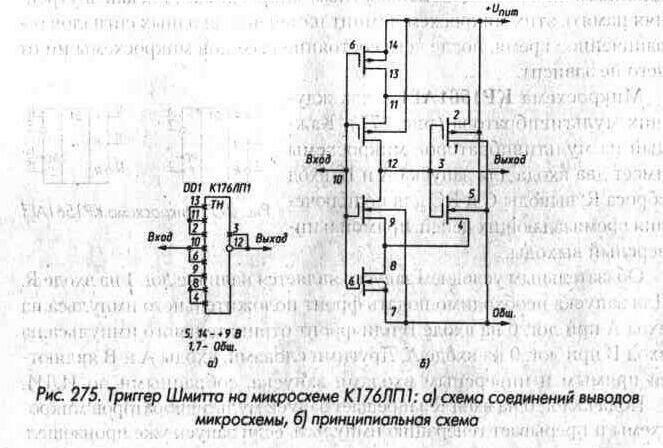

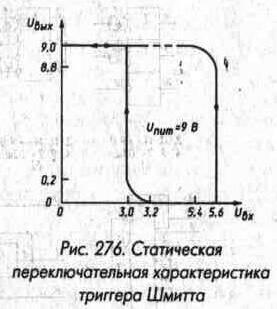

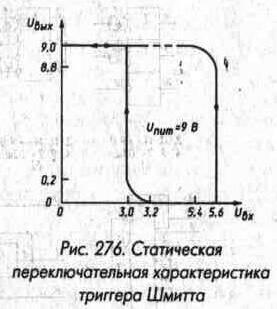

На рис. 275 приведена схема триггера Шмитта, который можно со-брать, используя микросхему К176ЛП1. Триггер состоит из двух сим-метричных половин, каждая из трех МОП-транзисторов с каналом р-типа или п-типа. Каждая из половин напоминает по построению

обычный триггер Шмитта на двух биполярных транзисторах, в котором эмиттерный резистор заменен на еще один МОП-транзистор, а в качестве нагрузочных резисторов использован триггер Шмитта на

транзисторах дополнительной структуры. На рис. 276 приведена переключательная характеристика триггера Шмитта.

Выходы большинства микросхем серий К176 и К561 (а у КР1561 -всех) дополнены буферными каскадами, поэтому перегрузка выходов сложных микросхем и даже замыкание выходов на общий провод или цепь питания не влияют на работу микросхем по другим выходам.

Кроме того, переключательные характеристики простых логических элементов имеют значительно более крутой средний участок, чем это показано на рис. 161. Поэтому, если по какой-либо причине необходима плавная переключательная характеристика, следует использовать микросхему К176ЛП1, включенную по одной из схем рис. 274 (а - д).

ИМС СА1 561 серии

К561СА1 и выводы микросхемы

делитель частоты на 7

имс 561ип1

исключающие"ИЛИ"

испльзование К176ЛП1

микросхема ЛС1

сравнение кодов

статическая характеристика триггера

структура К176ИП1

схема включения ИП2

схема на ИМС К561ИП2

триггер Шмидта